標題: 全國產RK3568J + FPGA的PCIe、FSPI通信實測數據分享! [打印本頁]

作者: Tronlong 時間: 2024-7-17 14:06

標題: 全國產RK3568J + FPGA的PCIe、FSPI通信實測數據分享!

本帖最后由 Tronlong 于 2024-7-22 10:48 編輯

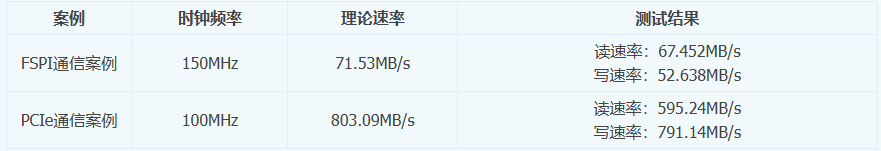

測試數據匯總

備注:

(1)當TLP header size =16Byte時,PCIe理論傳輸速率為:782.50MB/s;

(2)當TLP header size =12Byte時,PCIe理論傳輸速率為:803.09MB/s;

FSPI、PCIe總線介紹

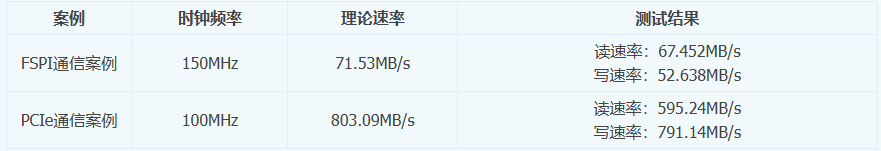

FSPI(Flexible Serial Peripheral Interface)是一種高速、全雙工、同步的串行通信總線,在RK3568J處理器中就有FSPI控制器,可用來連接FSPI設備。它具備如下特點:

(1)支持串行NOR FLASH、串行NAND FLASH;

(2)支持SDR模式;

(3)支持單線、雙線以及四線模式。

圖1 FSPI數據傳輸波形圖

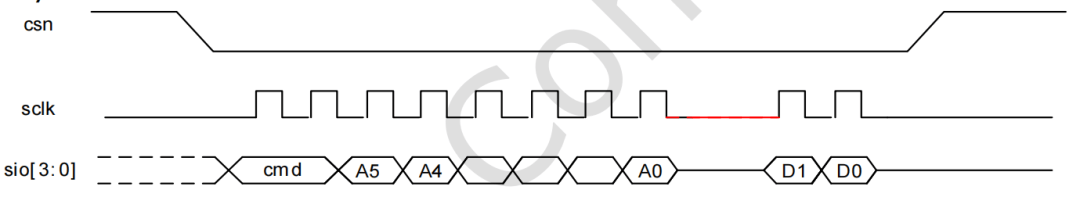

PCIe,即PCI-Express(peripheral component interconnect express)是一種高速串行計算機擴展總線標準。主要用于擴充計算機系統總線數據吞吐量以及提高設備通信速度。

圖2 PCIe數據傳輸圖

硬件平臺介紹

硬件方案:創龍科技TL3568F-EVM評估板(瑞芯微RK3568J + 紫光同創Logos-2)。

TL3568F-EVM評估板簡介:

創龍科技TL3568F-EVM是一款基于瑞芯微RK3568J/RK3568B2四核ARM Cortex-A55處理器 + 紫光同創Logos-2 PG2L50H/PG2L100H FPGA設計的異構多核國產工業評估板,由核心板和評估底板組成,ARM Cortex-A55處理單元主頻高達1.8GHz/2.0GHz。核心板ARM、FPGA、ROM、RAM、電源、晶振、連接器等所有元器件均采用國產工業級方案,國產化率100%。同時,評估底板大部分元器件亦采用國產工業級方案。

RK3568J + FPGA典型應用場景

RK3568J + FPGA應用場景十分廣泛,涵蓋小電流選線、繼電保護測試儀、運動控制器、醫療內窺鏡、血液分析儀、目標識別跟蹤等領域,可滿足多種工業應用要求。

圖3

案例測試

下文主要介紹基于瑞芯微RK3568J與紫光同創Logos-2(硬件平臺:創龍科技TL3568F-EVM評估板)的FSPI、PCIe通信案例,按照創龍科技提供的案例用戶手冊進行操作得出測試結果。

基于RK3568J + FPGA的FSPI通信案例

(1)案例說明

ARM端運行Linux系統,基于FSPI總線對FPGA DRAM進行讀寫測試。

圖4 ARM端程序流程圖

ARM端實現SPI Master功能,原理說明如下:

a)打開SPI設備節點,如:/dev/spidev4.0。

b)使用ioctl配置FSPI總線,如FSPI總線極性和相位、通信速率、數據長度等。

c)選擇模式為單線模式、雙線模式或四線模式。當設置FSPI為四線模式時,發送數據為四線模式,接收數據為四線模式。

d)發送數據至FSPI總線,以及從FSPI總線讀取數據。

e)校驗數據,然后打印讀寫速率、誤碼率。

FPGA端實現SPI Slave功能,原理說明如下:

a)FPGA將SPI Master發送的數據保存至DRAM。

b)SPI Master發起讀數據時,FPGA從DRAM讀取數據通過FSPI總線傳輸至SPI Master。

(2)測試結果

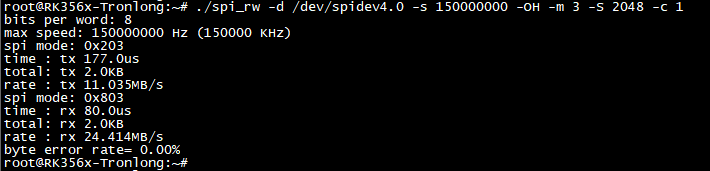

ARM通過FSPI總線(四線模式)寫入2048Byte隨機數據至FPGA DRAM,然后讀出數據、進行數據校驗,同時打印FSPI總線讀寫速率和誤碼率。

從下圖可知,本次實測寫速率為11.035MB/s,讀速率為24.414MB/s,誤碼率為0.00%。

圖5

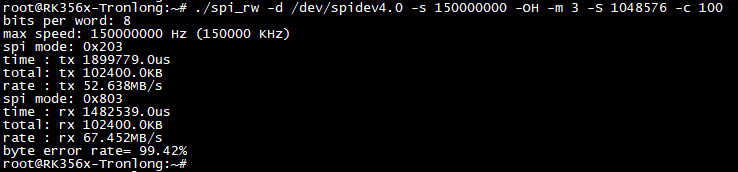

若設置FSPI總線通信時鐘頻率為150MHz,ARM通過FSPI總線寫入1MByte隨機數據至FPGA DRAM,然后讀出數據,循環100次,不做數據檢驗,最后打印FSPI總線讀寫速率和誤碼率。

最終,本次測試設置FSPI總線通信時鐘頻率為150MHz,則FSPI四線模式理論通信速率為:(150000000 / 1024 / 1024 / 8 x 4)MB/s ≈ 71.53MB/s。從下圖可知,本次實測寫速率為52.638MB/s,讀速率為67.452MB/s,比較接近理論通信速率。

備注:本案例設計FPGA BRAM大小2048Byte,一次寫入1MByte數據量會導致BRAM數據溢出,因此誤碼率較高。配置一次寫入1MByte數據量只是為了驗證FSPI的最大通信速率,不考慮誤碼率。

圖6

基于RK3568J + FPGA的PCIe通信案例

(1)案例說明

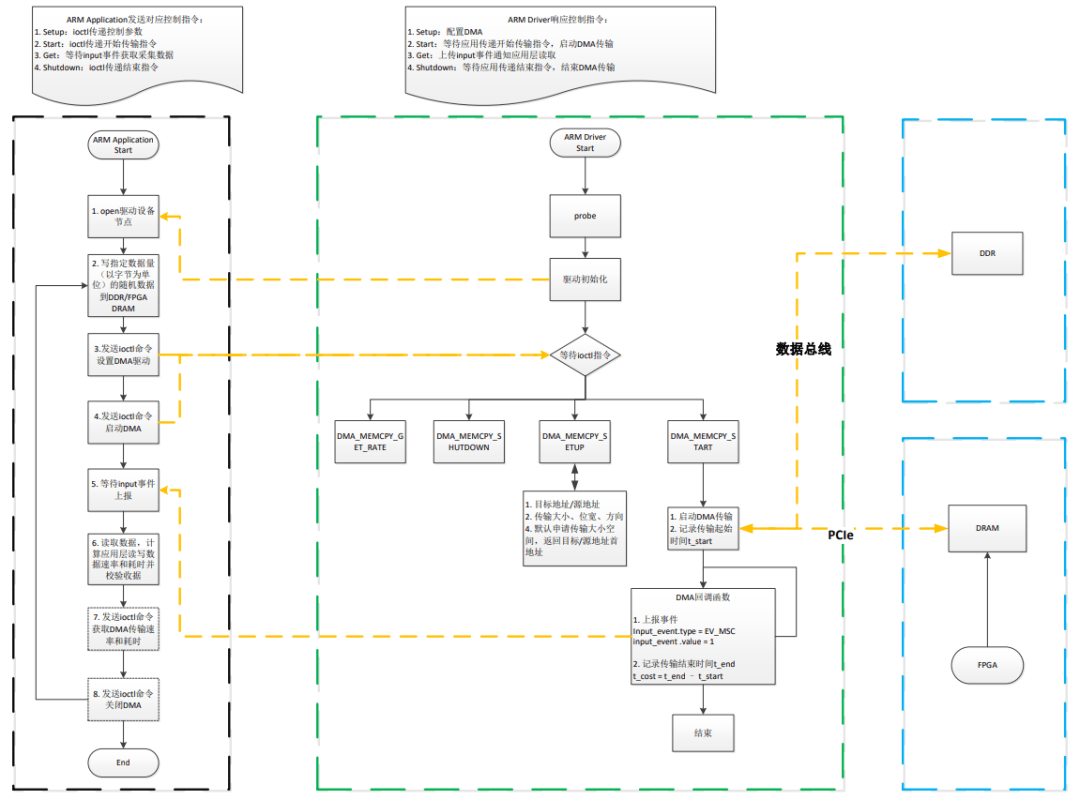

ARM端基于PCIe總線對FPGA DRAM進行讀寫測試。應用程序通過ioctl函數發送命令開啟DMA傳輸數據后,等待驅動上報input事件;當應用層接收到input事件,說明DMA傳輸數據完成。

圖7 程序流程圖

ARM端原理說明如下:

a)采用DMA方式;

b)將數據寫至dma_memcpy驅動申請的連續內存空間(位于DDR);

c)配置DMA,如源地址、目標地址、傳輸的數據大小等;

d)寫操作:通過ioctl函數啟動DMA,通過PCIe總線將數據搬運至FPGA DRAM;

e)程序接收驅動上報input事件后,將通過ioctl函數獲取DMA搬運數據耗時,并計算DMA傳輸速率(即寫速率);

f)讀操作:通過ioctl函數啟動DMA,通過PCIe總線將FPGA DRAM中的數據搬運至dma_memcpy驅動申請的連續內存空間(位于DDR);

g)程序接收驅動上報input事件后,將數據從內核空間讀取至用戶空間,然后校驗數據,同時通過ioctl函數獲取DMA搬運數據耗時,并計算DMA傳輸速率(即讀速率)。

FPGA端原理說明如下:

a)實現PCIe Endpoint功能;

b)處理PCIe RC端發起的PCIe BAR0空間讀寫事務;

c)將PCIe BAR0讀寫數據緩存至FPGA DRAM中。

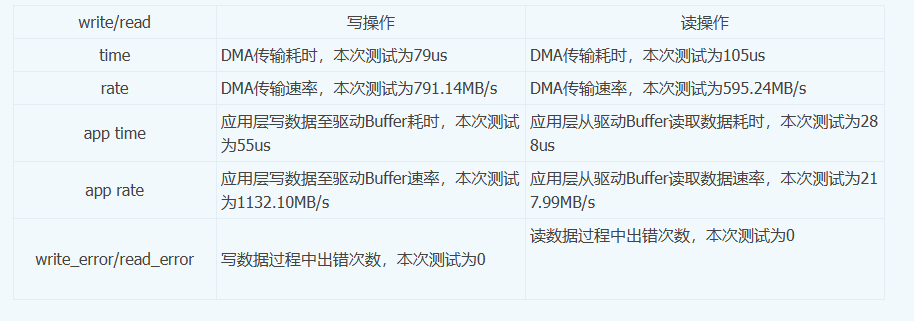

(2)測試結果

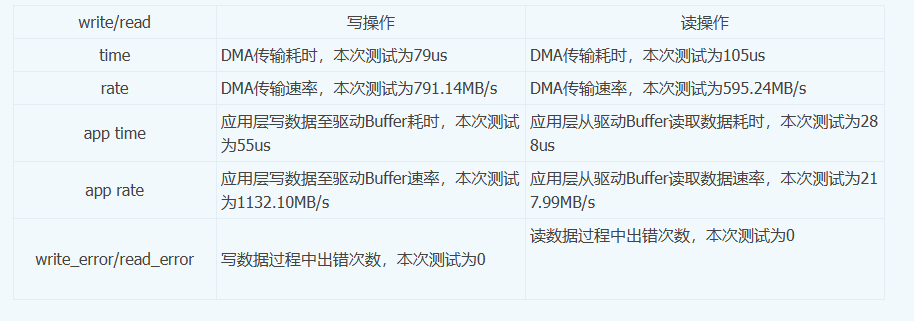

將隨機數據先寫入FPGA DRAM,再從FPGA DRAM讀出。測試完成后,程序將會打印最終測試結果,包含讀寫平均傳輸耗時、讀寫平均傳輸速率、讀寫錯誤統計等信息。

圖8

表 2 測試結果說明

| 歡迎光臨 (http://m.zg4o1577.cn/bbs/) |

Powered by Discuz! X3.1 |

主站蜘蛛池模板:

婷婷在线免费

|

亚洲成人毛片

|

在线中文视频

|

国产毛片视频

|

午夜精品久久久久久久久久久久

|

亚洲精品视频在线看

|

中文字幕视频网

|

日韩一区二区福利视频

|

国产精品久久久久久久久久三级

|

怡红院怡春院一级毛片

|

韩国精品在线

|

超碰在线播

|

国户精品久久久久久久久久久不卡

|

久久国产精品色av免费观看

|

亚洲人va欧美va人人爽

|

亚洲欧洲激情

|

91私密视频

|

91久色|

欧美中文一区

|

www.一级毛片

|

伊人伊人伊人

|

亚洲国产aⅴ成人精品无吗

欧美激情欧美激情在线五月

|

九九久久精品视频

|

欧美一区二区三区在线观看视频

|

人妖无码

|

在线视频国产一区

|

久久中文高清

|

在线看片网站

|

国产真实乱对白精彩久久小说

|

高清国产午夜精品久久久久久

|

逼逼视频

|

成人免费在线播放视频

|

中文一区

|

免费看片国产

|

久久久免费观看视频

|

亚洲 中文 欧美 日韩 在线观看

|

欧美精品一区二区在线观看

|

午夜专区|

国产精品特级毛片一区二区三区

|

在线观看黄色

|

亚洲精品一区二区三区四区高清

|