��(bi��o)�}: �T�ؕr(sh��)犺͕r(sh��)�ʹ�ܵ����� [��ӡ���]

����: 51��fan �r(sh��)�g: 2016-1-31 04:28

��(bi��o)�}: �T�ؕr(sh��)犺͕r(sh��)�ʹ�ܵ�����

����DEMOֱ�^��������ʹ�ܕr(sh��)犵�ʹ�ã�����һ��

�T�ؕr(sh��)�

�r(sh��)�ʹ���·��ͬ���O(sh��)Ӌ(j��)����Ҫ�����·���ںܶ��O(sh��)Ӌ(j��)�У��mȻ��(n��i)����ͬģ�K��̎���ٶȲ�ͬ�����������@Щ�r(sh��)���ͬԴ�ģ����Ԍ������D(zhu��n)�����һ�ĕr(sh��)��·̎������FPGA���O(sh��)Ӌ(j��)�У����l�r(sh��)犺�Դ�r(sh��)犵�skew�������ƣ��y�Ա��C���l�r(sh��)犺�Դ�r(sh��)�ͬ�ࡣ�ʴ����]����ʹ�Õr(sh��)�ʹ�ܵķ�����ͨ�^ʹ�Õr(sh��)�ʹ�ܿ��Ա���r(sh��)犡��M���w������r���M(j��n)�������˲���Ҫ�ā���(w��n)�B(t��i)�l(f��)�����ڽ����O(sh��)Ӌ(j��)��(f��)�s�ȵ�ͬ�r(sh��)Ҳ������O(sh��)Ӌ(j��)�Ŀɿ��ԡ�

�T�ؕr(sh��)� Verilogʾ�����a��

input wr_n; //��ʹ����̖������Ч

input cs_n; //Ƭ�x��̖������Ч

input[7:0] db; //ݔ�딵(sh��)��(j��)����

output db_r; //�i��ݔ��

reg db_r; //ݔ�딵(sh��)��(j��)�Ĵ���

wire d_clk; //�T�ؕr(sh��)���̖

assign d_clk = wr_n || cs_n;

always @ (posedge d_clk) //�T�ؕr(sh��)�������

db_r <= db; //�i��ݔ�딵(sh��)��(j��)

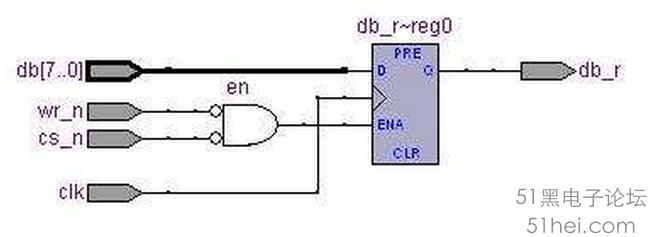

RTL Viewer:

�M��߉�ж����T�ؕr(sh��)犣�һ���(q��)��(d��ng)�T�ؕr(sh��)犵�߉����ֻ����һ��(g��)�c�T�����T��������������ĸ���߉���������a(ch��n)����ϣ����ë�̡�

ʹ�ܕr(sh��)�

Verilogʾ�����a��

input clk; //50MHz�r(sh��)���̖

input wr_n; //��ʹ����̖������Ч

input cs_n; //Ƭ�x��̖������Ч

input[7:0] db; //��(sh��)��(j��)����

output db_r;

reg db_r; //ݔ�딵(sh��)��(j��)�Ĵ���

wire en; //ʹ����̖

assign en = ~wr_n && ~cs_n;

always @ (posedge clk) //ȫ�֕r(sh��)�������

if(en) //ʹ���i��ݔ��

db_r <= db; //�i��ݔ�딵(sh��)��(j��)

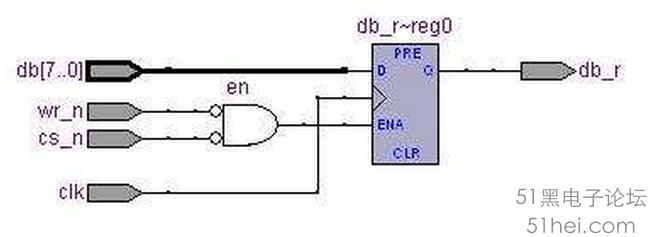

RTL Viewer:

ʹ�ܕr(sh��)��@Ҫ�����ڕr(sh��)��߉�У����T�ؕr(sh��)�Ҫ���ķ�(w��n)����

����ֻ��һ��(g��)�e������(sh��)�H��������(sh��)�F(xi��n)�Ĺ�����߀����һ�c(di��n)��e�ġ��T�ؕr(sh��)�һ�������܉���^��(zh��n)�_����wr_n���������i�攵(sh��)��(j��)�ġ���ʹ�ܕr(sh��)�һ������wr_n��Ч���g��ÿ��(g��)�r(sh��)����ڶ����i��ݔ�딵(sh��)��(j��)�������Y(ji��)�����i��Ĵ�����Ĕ�(sh��)��(j��)��wr_n����ǰ��0-T(T=1/clk)�r(sh��)�g��(n��i)�i��Ĕ�(sh��)��(j��)����?y��n)��ǂ�(g��)���ӣ�Ҳ�Ͳ�Ԕ��(x��)�f�����w��r���w������

��ijϵ�y(t��ng)�У�ǰ����(sh��)��(j��)ݔ��λ����8�����Ĕ�(sh��)��(j��)ݔ��λ��32���҂���Ҫ��8bit�Ĕ�(sh��)��(j��)�D(zhu��n)�Q��32bit�Ĕ�(sh��)��(j��)����˺�̎���ĕr(sh��)��l�ʞ�ǰ����1/4������ʹ�Õr(sh��)犕r(sh��)�ܣ��t��Ҫ��ǰ���r(sh��)��M(j��n)��4���l�������̎���ĕr(sh��)犣��@�N�O(sh��)Ӌ(j��)�����������µĕr(sh��)����˱����@�N��r���҂������˕r(sh��)犕r(sh��)�ܵķ�����p���O(sh��)Ӌ(j��)�ď�(f��)�s�ȡ�

module gray

(

input clk,

input rst_n,

input [7:0] data_in,

output reg [31:0] data_out,

output reg clk1x_en

);

reg [1:0] cnt;

reg [31:0] shift_reg;

always @ (posedge clk,negedge rst_n)

begin

if(!rst_n)

cnt <= 2'b0;

else

cnt <= cnt +1'b1;

end

always @ (posedge clk,negedge rst_n)

begin

if(!rst_n)

clk1x_en <= 1'b0;

else if(cnt ==2'b01)

clk1x_en <= 1'b1;

else

clk1x_en <= 1'b0;

end

always @ (posedge clk,negedge rst_n)

begin

if(!rst_n)

shift_reg <= 32'b0;

else

shift_reg <= {shift_reg[23:0],data_in};

end

always @ (posedge clk,negedge rst_n)

begin

if(!rst_n)

data_out<= 32'b0;

else if(clk1x_en==1'b1)//�H��clk1x_en��1�r(sh��)�Ō�shift_reg��ֵ�x�odata_out

data_out<=shift_reg;

end

endmodule

| �gӭ���R (http://m.zg4o1577.cn/bbs/) |

Powered by Discuz! X3.1 |

��վ֩���ģ�壺

性爱免费视频

|

91久色|

日韩精品久久久久久

|

国产精品二区一区二区aⅴ污介绍

|

国产日韩久久

|

欧美一区二区

|

夜夜欢视频

|

亚洲精品aaa|

欧美a视频|

国产精品成人国产乱

|

亚洲国产精品久久

|

久久不卡视频

|

欧美伊人久久

|

网站av|

一级a毛片|

四虎影视大全

|

五月激情久久

|

伦一理一级一a一片

|

国产在线一区二区

|

国产在线日韩

|

天天操狠狠干

|

久久久久久91

|

久久中文视频

|

伊人久久久久久久久久

|

九九综合网|

久久精品在线

|

欧美大白屁股

|

日本一级大毛片a一

|

人人超碰在线

|

成人午夜在线视频

|

免费看黄色小视频

|

国产精品久久久久久久久久久久久

|

亚洲精品1区2区

|

久色精品|

一级做a视频|

免费一区二区视频

|

成人免费福利视频

|

欧美特黄

|

免费成人深夜夜行网站

|

老熟女毛片

|

懂色av一区二区三区

|