|

發布時間: 2025-7-17 15:23

正文摘要:看到公司里用fmd芯片驅動mos都是io直連柵極再加一個5V上拉電阻的連接方式,這種芯片數據手冊里只說了有設置輸入或者輸出和輸入弱上拉的功能,沒具體寫輸出是什么模式,是因為是開漏輸出還是驅動能力不夠所以需要這么 ... |

JRNitre 發表于 2025-7-19 20:56 你知道 Vgsth 是什么意思嗎?threshold是什么意思?datasheet里面 Vgsth =1.2 同時標注了此時Id=250uA,這是導通嗎? |

| STC的MCU,IO設置為推挽輸出,串聯一個200~1K電阻到柵極,不需要上拉電阻。IO上電是高阻,MOS輸入也是高阻,所以要下拉一個10~20K電阻以確定上電時MOS不導通。 |

| 有沒有可能是芯片上電初始化這個時間給外部一個確定的電平信號 |

|

就一個LED不需要驅動, 90%以上的CPU-GPIO口都可以直驅,3.3v供電的限流小點而已。 |

| 這 MOS 的 Vgsth 最大才 1.2v 你 MCU 輸出電平肯定大于這個標準,推挽驅動就行,你這 MOS 驅動也不對開啟時間敏感 |

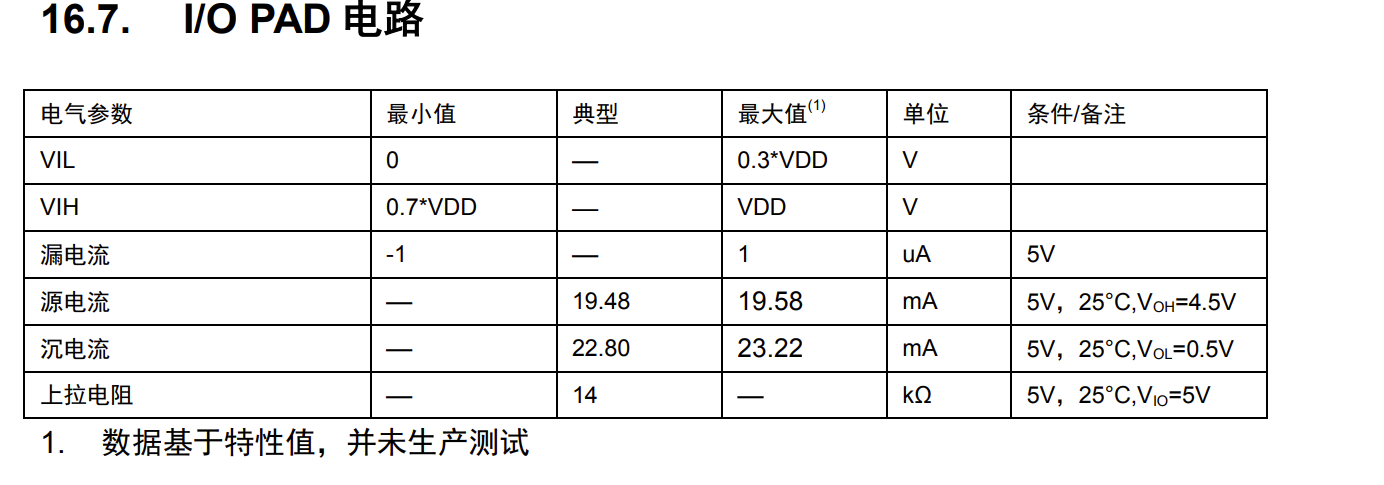

| datashheet里面15.7. I/O PAD電路這張表格寫的很清楚了。 |

| 型號是ft60e023,圖1寫著源電流有20mA,感覺是推挽輸出,但如果是推挽輸出感覺不加5v也可以。現在弄燈板如果加這5v就要5p排線,如果能直接連不加上拉就能用4p線了 |