本帖最后由 電子愛好者沒錯 于 2023-8-22 20:07 編輯

FPGA 開發專題 | 初識 FPGA 開發流程和仿真工具

目錄:

- 一、FPGA 開發流程

- 二、FPGA 仿真工具

- 三、開設 FPGA 專題咯D:\Xzhao\Documents\OfficialAccounts\Article\2023.07.01\photos\Apolong_at_Shougang_Jiaohuachang_(20230322140939).jpg

圖:北京首鋼園內的無人駕駛小巴士

全文 2031 字,閱讀大約需要 4 分鐘

第一臺真正意義上的自動駕駛汽車最早可追溯至 1980 年代,隨著近年來人工智能和新型傳感器(硬件)的快速發展,自動駕駛相關行業迅速進入紅海。盡管相關技術已經逐步趨于成熟,但如何更快地識別路況、提高系統判別實時性一直是學術界和工業界追求的目標。 FPGA 作為一種半定制化電路,具有 ASCII 芯片所沒有的可編程的靈活性,又具有一般 CPU 所不具備的硬件層并行數據處理的優勢,廣泛用于圖像處理、機器視覺、無人駕駛等領域。在某種程度上,FPGA 可兼顧人工智能的大量計算需求和工業應用中低延時的要求。從前幾年神經網絡軟件算法的爆火到近些年來 “用 FPGA 加速神經網絡 ” 逐漸火出圈,讓我們看到了技術發展自上而下的革新,從軟件到硬件,從高層抽象到底層電路,硬件的天花板作用越發彰顯。

本文首發于在下石同學 未經授權 不得轉載

文 | 在下石同學

一、FPGA 開發流程 FPGA (Field Programmable Gate Array),即現場可編程邏輯陣列。

現場可編程邏輯門陣列(Field Programmable Gate Array,縮寫為FPGA),它以PAL、GAL、CPLD等可編程邏輯器件為技術基礎發展而成。作為特殊應用集成電路中的一種半定制電路,它既彌補全定制電路不足,又克服原有可編程邏輯控制器邏輯門數有限的缺點。

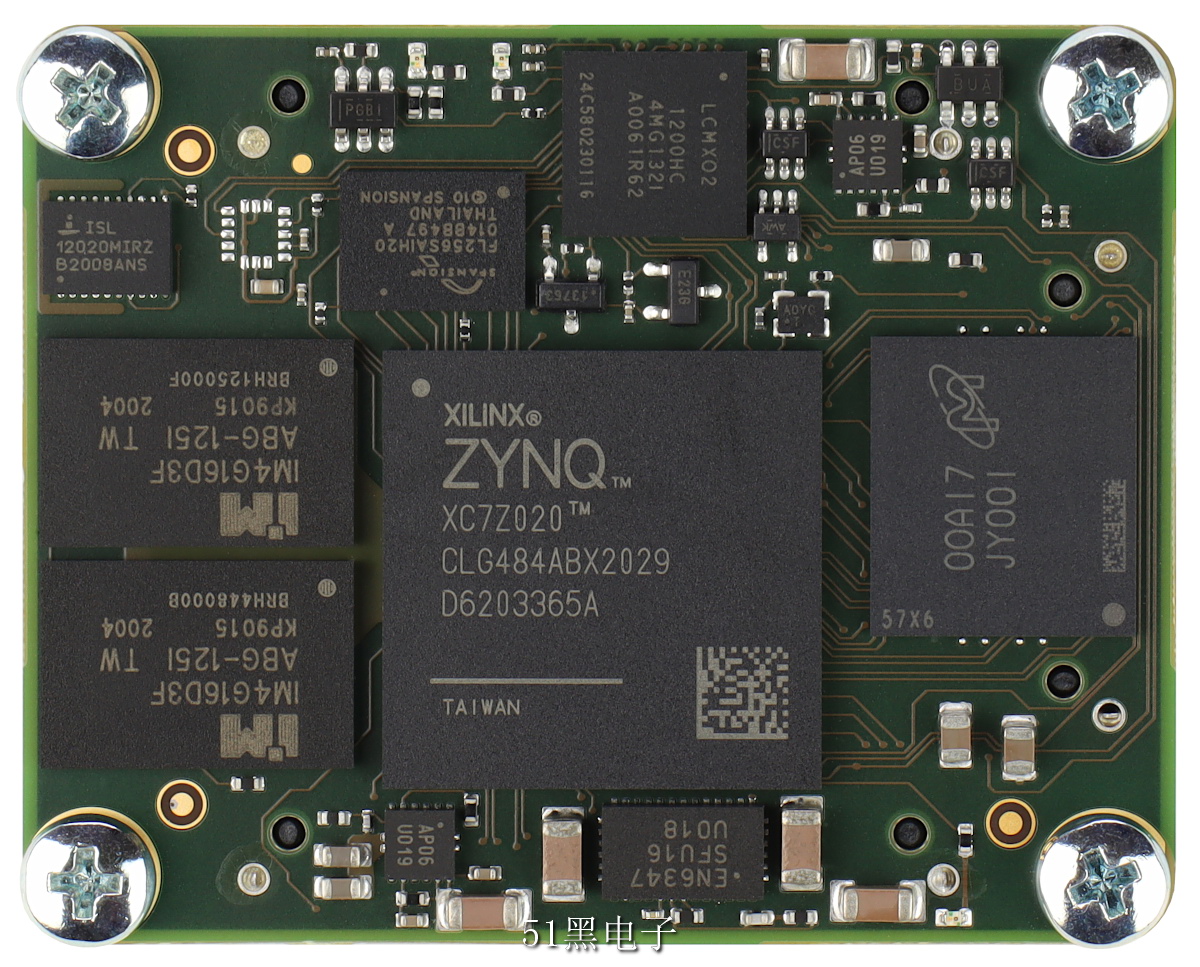

圖:ZYNQ-7020 核心板

FPGA 作為一種半定制化電路,具有 ASCII 芯片所沒有的可編程的靈活性,又具有一般 CPU 所不具備的硬件層并行數據處理的優勢,廣泛用于圖像處理、機器視覺、無人駕駛等領域。在某種程度上,FPGA 可兼顧人工智能的大量計算需求和工業應用中低延時的要求。從前幾年神經網絡軟件算法的爆火到近些年來 “用 FPGA 加速神經網絡 ” 逐漸火出圈,讓我們看到了技術發展自上而下的革新,從軟件到硬件,從高層抽象到底層電路,硬件的天花板作用越發彰顯。

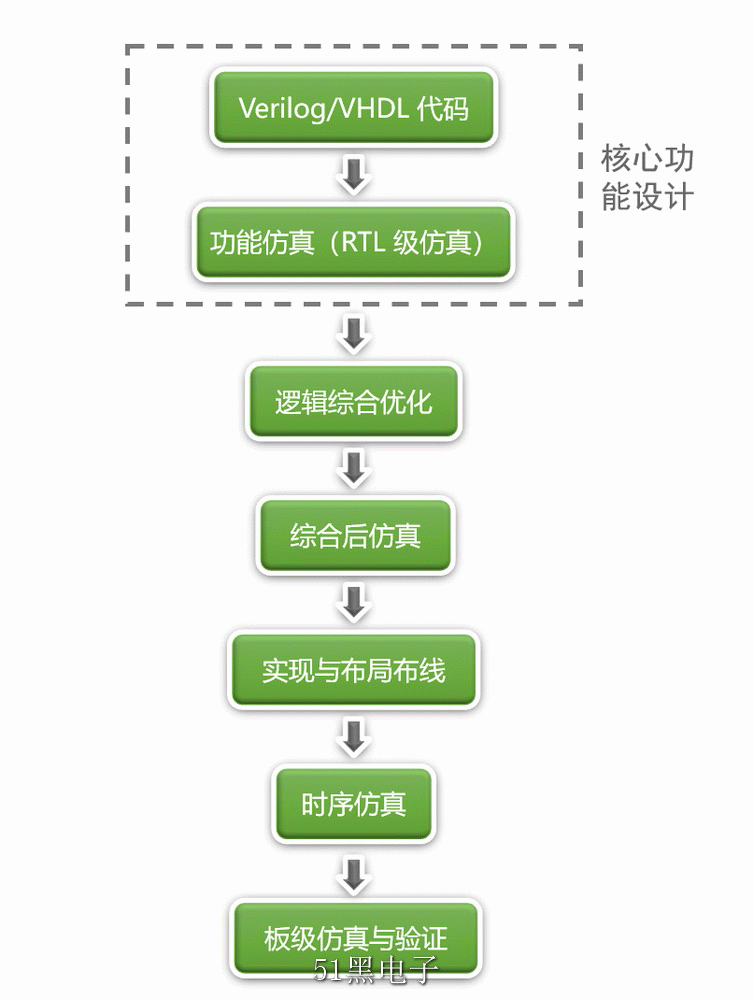

相對于一般編程語言開發,FPGA 的開發過程更為繁瑣,盡管 FPGA 也有 Verilog/VHDL 這樣的代碼語言去描述和定義邏輯功能,但 Verilog/VHDL 是硬件描述語言,跟 C/C++ 不同的是,經過后續的綜合以后,可以直接生成對應的電路。 FPGA 的開發流程主要包括 7 個部分,如下圖所示:

圖:FPGA 開發流程 下面簡要聊聊各個部分的作用(敲重點!)

- Verilog/VHDL 代碼:我們使用硬件描述語言去編寫對應的電路模塊,實現邏輯功能,這部分是整個設計中占比最大的一環

- RTL 級仿真:這部分是功能仿真,類似于 C/C++ 開發中的 debug 功能,我們需要對寫好的 Verilog/VHDL 代碼進行測試和檢查,以驗證我們的功能模塊沒有出現邏輯錯誤,一般會編寫 Testbench 代碼并編譯生成波形文件,通過波形文件就可以判斷邏輯功能是否有誤

- 邏輯綜合優化:綜合是將上述過程中較為高級的硬件描述語言轉化為更為底層的實現,最終編譯成由與/或/非門、RAM、觸發器等基本邏輯單元組成的網表,但并不代表真實的門電路

- 綜合后仿真:只考慮邏輯和功能的實現是不嚴謹的,實際上真實門電路的信號傳輸一定伴隨著延時,會導致各種競爭冒險和時序紊亂的現象發生,這部分會把標準的延時參數送入仿真模型中二次核驗,更加貼近真實情況

- 實現與布局布線:通過以上過程已經得到了電路的網表,實現和布局布線的過程就是把網表配置到具體的 FPGA 芯片中

- 時序仿真:也稱為后仿真,時序仿真把上一步布局布線的延時都考慮進去,并標注到網表中,是芯片延時信息的最真實、最準確的反映

- 板級仿真與驗證:一般用于高速信號,對信號完整性等進行綜合分析

我們可以看到,FPGA 的開發過程是非常折騰的,通過 RTL 級仿真、綜合后仿真、時序仿真三大仿真實現從邏輯到門電路時延的反饋和調整,好在大部分工作都由 EDA 軟件工具幫我們完成了,實際上,在大部分開發中,整個流程中最核心的還是前兩部分,Verilog/VHDL 代碼和RTL 級仿真。

二、FPGA 仿真工具 FPGA 的仿真工具有很多,但由于 FPGA 芯片本身專利問題及制造的差異性,基本上某一具體型號 FPGA 芯片的開發工具和該器件廠商是綁定的,不像 ARM 這種嵌入式通用處理器有更加完善和通用的開發工具鏈。當然,對于一般 Verilog/VHDL 的 RTL 級層面仿真,不涉及具體的芯片型號,市面上的仿真工具都可以使用,常見的如大牌廠商 Altera(現已被 Intel 收購)家的 Quartus,Xilinx 家的 Vivado,Mentor Graphics 家的 ModelSim,Cadence 家的 NCSim,開源的 Icarus Verilog 以及一些國產方案等。

注:本文用到的所有軟件相關參考鏈接都會附在文末 工具 | 廠商 | 說明 | Quartus | Altera |

| Vivado | Xilinx |

| ModelSim | Mentor Graphics | PE、DE、SE 三個版本,非常流行 | NCSim | Cadence | Incisive 工具套件,用于 ASIC 設計 | Icarus Verilog | GNU GPL | 開源、輕量 | TangDynasty | 上海安陸科技 | 國產廠商 | Pango Design Suite | 紫光同創(深圳) | 國產廠商 | procise | 復旦微(上海) | 國產廠商 |

Altera 和 Xilinx 家的 FPGA 是市場占有率最高的,涵蓋了 FPGA 設計的整個流程,ModelSim 是 FPGA 仿真最受歡迎的軟件,非常流行, Icarus Verilog 支持 GPL 協議,開源免費且輕量,也是 FPGA 開發中 RTL 級仿真值得使用的軟件,搭配 GTKwave,出仿真圖非常方便,功能強大。

三、開設 FPGA 專題咯 本文簡單介紹了 FPGA 開發的基本流程和常見的仿真工具,太長時間沒更新了所以趕緊水一篇。 開設 FPGA 專題咯,就當作 FPGA 專題的開篇吧!

文中涉及 FPGA 軟件工具參考網站:

除了在51黑電子論壇發帖,大家也可以關注我的微信公眾號:在下石同學

讓技術有深度,讓科普有溫度~ 旨在分享電子電路、嵌入式、編程相關的筆記和教程,包括:電子電路設計、PCB設計、通信協議、嵌入式編程等。還會不定期分享有趣好玩的開源項目 平時學習工作很忙,偶爾鴿一下~ 會堅持更新的!

微信掃碼可以關注我的公眾號(哈哈純技術分享,不存在任何打廣告行為,放心食用):

|