늙C(j��)��һ�N�����D(zhu��n)�Q���b�ã��ڇ���(j��ng)��(j��)��������Ҫ���ã��oՓ���ڹ��r(n��ng)���a(ch��n)����ͨ�\(y��n)ݔ����������t(y��)���l(w��i)�����̄�(w��)�c�k���O(sh��)�䣬߀���ճ������еļ����������������ʹ�������N���ӵ�늙C(j��)������܇���ҕ�C(j��)����L(f��ng)�ȡ����{(di��o)�ȵ�Ҳ�x���_늙C(j��)��ͬ�r����Խ��Խ��đ�(y��ng)�È��ϣ�ֻ�����D(zhu��n)��늙C(j��)���o���M��Ҫ����Ҫ���܉�?q��)��F(xi��n)���ټ��١��p�ٻ��D(zhu��n)�Լ���(zh��n)�_ֹͣ�ȹ��ܡ���회����µ�늙C(j��)���������m��(y��ng)�r���İl(f��)չ��

늙C(j��)�Ŀ�������(j��ng)�v�ˏ�ģ�M����������(sh��)�ֿ������İl(f��)չ������ģ�M�����ą���(sh��)�����Ӱ푴��Ҿ���Ҳ�^���(sh��)�ֿ������cģ�M����������^�����пɿ��Ըߡ�����(sh��)�{(di��o)�����㡢���ƾ��ȸߡ����h(hu��n)�����ز����еȃ�(y��u)�c(di��n)���S�����I(y��)늚⻯���Ԅӿ��ƺͼ�늮a(ch��n)Ʒ���I(l��ng)��?q��)�늙C(j��)���Ʈa(ch��n)Ʒ�������˂���늙C(j��)���Ƽ��g(sh��)��Ҫ��������ߡ����ڂ��y(t��ng)��8λ��Ƭ�C(j��)���(n��i)���wϵ�Y(ji��)��(g��u)��Ӌ(j��)�㹦�ܵȗl�����ƣ��ڌ�(sh��)�F(xi��n)���N���M(j��n)��늙C(j��)������Փ��Ч�Ŀ����㷨�r���������y����ˣ�Ŀǰ����ձ��������ʹ�ø����ܵĔ�(sh��)����̖̎����(DSP)����Q늙C(j��)�������������ӵ�Ӌ(j��)�������ٶȵ�����һϵ������O(sh��)����ģ��(sh��)�D(zhu��n)�Q�����}���{(di��o)�ưl(f��)�������͔�(sh��)����̖̎����������һ��M�ɏ�(f��)�s��늙C(j��)����ϵ�y(t��ng)���S��EDA���g(sh��)�İl(f��)չ���û��ڬF(xi��n)���ɾ����T���FPGA�Ĕ�(sh��)�����ϵ�y(t��ng)��늙C(j��)�M(j��n)�п��ƣ��錍(sh��)�F(xi��n)늄әC(j��)��(sh��)�ֿ����ṩ��һ�N�µ���Ч�������F(xi��n)���ɾ����T���(FPGA)�������ɶȸߡ��w�eС���ٶȿ죬��Ӳ���·��(sh��)�F(xi��n)�㷨����ԭ�����·�弉�a(ch��n)Ʒ���ɞ�оƬ���a(ch��n)Ʒ���Ķ������˹��ģ�����˿ɿ��ԡ�

늄әC(j��)�{(di��o)��ϵ�y(t��ng)����FPGA��(sh��)�F(xi��n)��(sh��)�ֻ�����,��늚���Ӱl(f��)չ����Ҫڅ�ݡ�����FPGA���ƺ�,�����{(di��o)��ϵ�y(t��ng)�܉�?q��)��F(xi��n)���ټ��١��p�ٻ���/���D(zhu��n)�Լ���(zh��n)�_ֹͣ���ھ��{(di��o)�ٵȹ���,�����S�o(h��)����,늄әC(j��)��(w��n)�B(t��i)�\(y��n)�D(zhu��n)�r�D(zhu��n)�پ��ȿ��_(d��)���^��ˮƽ,�o�ӑB(t��i)���(xi��ng)ָ��(bi��o)�����^�õ؝M�㹤�I(y��)���a(ch��n)�и�����늚���ӵ�Ҫ������FPGA�� �ⲿ�B����,�·����,���ڿ���,�����^�ѵ����܃r(ji��)���,�����ڹ��I(y��)�^�̼��O(sh��)������еõ�����V���đ�(y��ng)��[1]��

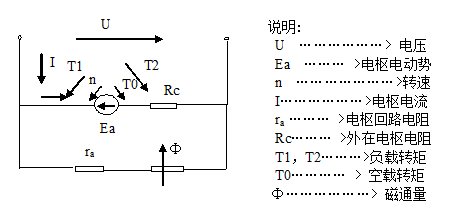

ֱ��늙C(j��)�����(sh��)����PWM���}���{(di��o)�ƣ��ķ����M(j��n)�п��ƣ����ЃɷNģʽ��һ�N�Dz���ģ�M�·���ƣ���һ�N�Dz��Ô�(sh��)�ֵĿ��ơ�ģ�M�����������{(di��o)ԇ��(f��)�s�ȹ���ԭ������u����̭�����ڔ�(sh��)�ֿ��Ƽ��g(sh��)�У�F(xi��n)PGA�Ĕ�(sh��)��PWM���ƾ��о��ȸߣ�����(y��ng)�죬�ⲿ�B���٣��·���Σ����ڿ��Ƶȃ�(y��u)�c(di��n)�V���ı��˂�ʹ�ã���(y��ng)���о�FPGA����ʮ����Ҫ�����x�����ڱ����O(sh��)Ӌ(j��)Ŀ�����ڣ�

��1�����ջ���FPGA��ֱ��늙C(j��)PWM����ԭ�����W(xu��)����(y��ng)��EDA���g(sh��)�M(j��n)�о���

��2��ͨ�^�����n�}���о�,����EDA�_�l(f��)���g(sh��)�ľ��̷��������B(y��ng)��(chu��ng)�����R����Փ(li��n)ϵ��(sh��)�H�ČW(xu��)�L(f��ng)����Ϥ�F(xi��n)����Ӯa(ch��n)Ʒ���O(sh��)Ӌ(j��)���̡�

FPGA���ڿ����I(l��ng)���e��늙C(j��)����߀�DZ��^�ٵģ����O(sh��)Ӌ(j��)��늙C(j��)����ϵ�y(t��ng)�ṩһ�N�Ŀ��Ƽ��g(sh��)����늙C(j��)���Ʒ�������һЩƬ��(n��i)ϵ�y(t��ng)�ij����о������O(sh��)Ӌ(j��)����ALTERA��˾��FPGAоƬ��FLEX10K10����Ŀ��(bi��o)����������ֱ��늙C(j��)���v����MAX+Plus II�O(sh��)Ӌ(j��)���̣������ˬF(xi��n)����Ӯa(ch��n)Ʒ���O(sh��)Ӌ(j��)�������������о���FPGA�a(ch��n)��PWM��̖�ķ�����

���O(sh��)Ӌ(j��)��늙C(j��)������ʹ�õ�һЩ�������ܱM���ܵؼ�����һƬF(xi��n)PGA�ϣ����O(sh��)Ӌ(j��)Փ��������FPGA��ֱ��늙C(j��)�M(j��n)�п��ƕr����ĸ����ֹ��ܡ�PWM���Įa(ch��n)�����ھ��{(di��o)�١����������߉��������Ӳ�������Z�Ԍ�PWM����FPGA���M(j��n)�нM��߉׃�Q�����M(j��n)�з��档

�ڇ��⣬PWMԴ�������o(j��)��ʮ�������˼��Դ��ͨ�ż��g(sh��)�����S���F(xi��n)����Ӽ��g(sh��)�İl(f��)չʹ��PWM��ՓԽ��Խ���죬��l(f��)չ���ٶ�Խ��Խ���١��ѽ�(j��ng)ȡ�����y(t��ng)�Ŀɿع�늙C(j��)�{(di��o)��ϵ�y(t��ng)����ԭ�ȵġ�늙C(j��)���ơ���늚���ӡ��Ѱl(f��)չ�����\(y��n)�ӿ��ơ������A�Ρ�IGBT�����MOSFET�Ȟ������ȫ���������IJ������ƽoPWM���Ƽ��g(sh��)�ṩ�ˏ�(qi��ng)������|(zh��)���A(ch��)��

�ڇ���(n��i)PWM����Փ���A(ch��)��u���죬���ڑ�(y��ng)���ϣ�����(n��i)����Ҳ�ܴ�PWM�{(di��o)��ϵ�y(t��ng)�đ�(y��ng)���ǽ�������_ʼ�ģ�ԭ�����҇�����ӹ��I(y��)�Ļ��A(ch��)���^�PWM�{(di��o)��ϵ�y(t��ng)��������P(gu��n)�I����IGOT�ܿ��M(j��n)�ڡ���������҇����_�l(f��)����������֪�R�a(ch��n)��(qu��n)��IGOT��������w�ܣ��Ķ���ԓ���g(sh��)���е춨�����|(zh��)���A(ch��)��PWM늙C(j��)�{(di��o)�ٷ�����δ��늙C(j��)�τ�ϵ�y(t��ng)�����x�������nj�(sh��)�F(xi��n)늙C(j��)�τӔ�(sh��)�ֿ��ƵĻ��A(ch��)[2]��

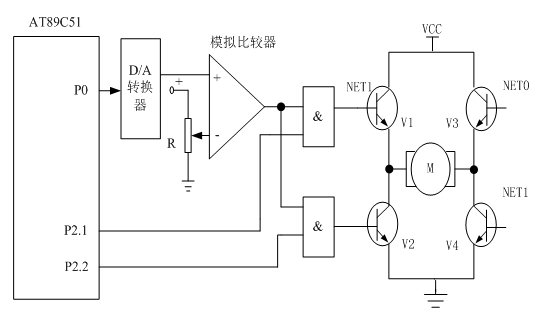

���O(sh��)Ӌ(j��)����˃ɷN���Ʒ�����һ�N�ǻ��چ�Ƭ�C(j��)��ֱ��늙C(j��)���ƣ���һ�N�ǻ���FPGA��ֱ��늙C(j��)���ƣ�ͨ�^������Փ�C�c���^�����ú����{(di��o)�ٷ�����

���O(sh��)Ӌ(j��)����Ҫ��(n��i)�������ջ���FPGA��ֱ��늙C(j��)PWM����ԭ�����O(sh��)Ӌ(j��)������/���D(zhu��n)����/ͣ���ƹ��ܡ��ٶ��ھ����{(di��o)��ֱ��늙C(j��)�����b�á�ͨ�^��ֱ��늙C(j��)���Ƶ��о�������EDA�_�l(f��)���g(sh��)��

���O(sh��)Ӌ(j��)Ԕ��(x��)�ķ�����ֱ���ĽY(ji��)��(g��u)����Ҫ���g(sh��)����(sh��)������ԭ�����{(di��o)��ԭ��������FPGA��PWM���ήa(ch��n)�����^�̣�����VHDL����PWM���Ρ����O(sh��)Ӌ(j��)�����й��ܾ���ALTERA��˾��MAX+Plus IIܛ����ͨ�^���档���O(sh��)Ӌ(j��)��PWM���Δ�(sh��)��(j��)�M(j��n)�Мyԇ�cԔ��(x��)�ķ�����

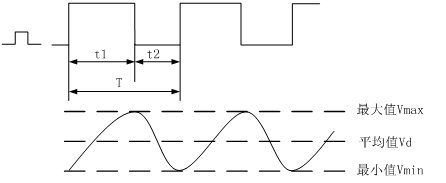

�乤��ԭ���ǣ��O(sh��)��ֵӋ(j��)��(sh��)�����O(sh��)��PWM��ռ�ձȡ���(d��ng)U/D=1�r,ݔ��CLK2,ʹ�O(sh��)��ֵӋ(j��)��(sh��)����ݔ��ֵ����, PWM��ռ�ձ�����,늙C(j��)�D(zhu��n)�ټӿ�;��(d��ng)U/D =0�r��ݔ��CLK2��ʹ�O(sh��)��ֵӋ(j��)��(sh��)����ݔ��ֵ�pС,PWM��ռ�ձȜpС,늙C(j��)�D(zhu��n)��׃����

��CLK0��������,��X��Ӌ(j��)��(sh��)��ݔ�������Ծ������ӵ���X������(d��ng)Ӌ(j��)��(sh��)ֵС���O(sh��)��ֵ�r,��(sh��)�ֱ��^��ݔ�����ƽ;��(d��ng)Ӌ(j��)��(sh��)ֵ�����O(sh��)��ֵ�r,��(sh��)�ֱ��^��ݔ�����ƽ,�ɴˮa(ch��n)�������Ե�PWM���Ρ�

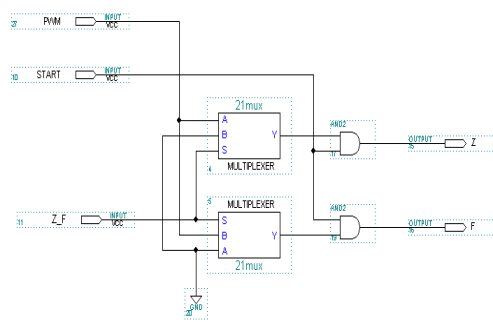

���D(zhu��n)��������·����ֱ��늄әC(j��)�D(zhu��n)��͆�/ͣ,ԓ�·�Ƀɂ�2�x1�Ķ�·�x�����M��,Z/F�I�����x��PWM�����Ǐ�����Z�M(j��n)��H��߀�Ǐ�ؓ(f��)��F�M(j��n)��H���Կ���늙C(j��)�����D(zhu��n)����(d��ng)Z/F=1�r��PWMݔ�����Ώ�����Z�M(j��n)��H��늙C(j��)���D(zhu��n)����(d��ng) Z/F =0�r��PWMݔ�����Ώ�ؓ(f��)��F�M(j��n)��H��늙C(j��)���D(zhu��n)��

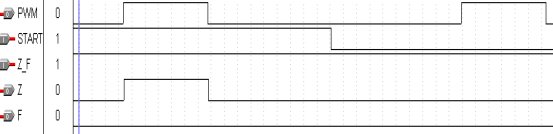

Start�Iͨ�^���c���T����PWMݔ��,��(sh��)�F(xi��n)��늙C(j��)�Ĺ���ֹͣ/���ơ���(d��ng)START=1�r���c�T���_�����S늙C(j��)��������(d��ng)START=0�r���c�T�P(gu��n)�]��늙C(j��)ֹͣ�D(zhu��n)�ӡ�

H���·�ɴ��ʾ��w�ܽM�ɣ�PWMݔ������ͨ�^��������·�͵� H ��, ��(j��ng)���ʷŴ��Ժ�ֱ��늙C(j��)��(sh��)�F(xi��n)�������\(y��n)�С�����EN1��̖�����Ƿ����S׃��[4]��

�c���چ�Ƭ�C(j��)��ֱ��늙C(j��)PWM�{(di��o)�ٷ�����ȣ�����FPGA��ֱ��늙C(j��)PWM����ʡȥ����ӵ�D/A�D(zhu��n)�Q����ģ�M���^����F(xi��n)PGA�ⲿ�B�����٣��·���Ӻ��Σ����ڿ��ơ�����FPGA��ֱ��늙C(j��)PWM���ƾ��о��ȸߣ�����(y��ng)�죬�ⲿ�B���٣��·���Σ����ڿ��Ƶȃ�(y��u)�c(di��n)����˱��O(sh��)Ӌ(j��)���û���FPGA��ֱ��늙C(j��)PWM���Ʒ���[2]��

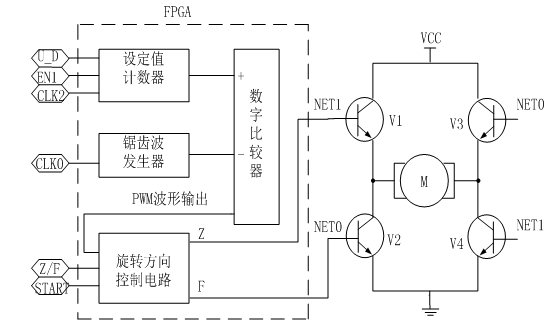

��D3.1��ʾ������FPGA��ֱ��늙C(j��)PWM�����·��Ҫ���IJ��ֽM�ɣ���������ݔ��ģ�K����������̎��ģ�K����������ݔ��ģ�K���Դģ�K���I�P�·���r��·��ϵ�y(t��ng)�Ŀ�������ݔ��ģ�K����FPGAоƬ�l(f��)�����F(xi��n)PGAоƬ��ϵ�y(t��ng)���������̎��ģ�K��ؓ(f��)؟(z��)���ա�̎��ݔ��������������ݔ��ģ�K�l(f��)��PWM��̖����ϵ�y(t��ng)�Ŀ��ƺ��ġ���������ݔ��ģ�K��H�͘�ʽֱ��늙C(j��)�(q��)���·�M�ɣ���ؓ(f��)؟(z��)������FPGAоƬ�l(f��)����PWM��̖���Ķ�����ֱ��늙C(j��)�������D(zhu��n)�������Լ��ھ��{(di��o)�١��Դģ�Kؓ(f��)؟(z��)�o�����·��늣����C�·�܉��������\(y��n)�С�

�ڈD3.1����ʾ��FPGA�Ǹ���(j��)�O(sh��)Ӌ(j��)Ҫ���O(sh��)Ӌ(j��)�õ�һ��оƬ�����(n��i)��߉�·��D4.1��

START��늙C(j��)���_���ˣ�U_D����늙C(j��)�����c�p�٣�EN1�����O(sh��)��늙C(j��)�D(zhu��n)�ٵij�ֵ��Z_F��늙C(j��)�ķ���˿ڣ��x��늙C(j��)�\(y��n)�еķ���CLK2��CLK0���ⲿ�r状ˣ�����Ҫ��������FPGA����ϵ�y(t��ng)�ṩ�r��}�_������늙C(j��)�M(j��n)���\(y��n)�D(zhu��n)��

ͨ�^�I�P�O(sh��)��PWM��̖��ռ�ձȡ���(d��ng)U_D=1�r, �����IU_D���£�ݔ��CLK2ʹ늙C(j��)�D(zhu��n)�ټӿ죻��(d��ng)U/D =0�������IU_D���_,ݔ��CLK2ʹ늙C(j��)�D(zhu��n)��׃�����@�ӾͿ��Ԍ�(sh��)�F(xi��n)늙C(j��)�ļ����c�p�١�

Z_F�I��늙C(j��)�\(y��n)�D(zhu��n)�ķ����I����(d��ng)��Z_F�I���r��Z_F=1��늙C(j��)���D(zhu��n)����֮Z/F =0�r��늙C(j��)���D(zhu��n)��

START��늙C(j��)���_���I����(d��ng)START=1�����S늙C(j��)��������(d��ng)START=0�r��늙C(j��)ֹͣ�D(zhu��n)�ӡ�

H���·�ɴ��ʾ��w�ܽM�ɣ�PWMݔ������ͨ�^�Ƀɂ����xһ�·�M�ɵķ�������·�͵� H ��, ��(j��ng)���ʷŴ��Ժ�ֱ��늙C(j��)��(sh��)�F(xi��n)�������\(y��n)�С�����EN1��̖�����Ƿ����S׃��[5]��

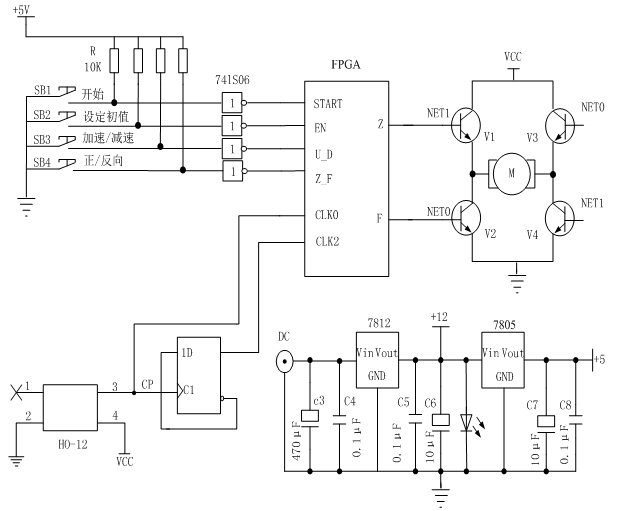

�I�P�·�ЃɷN��ͣ�����һ�N�Ǫ�(d��)��ʽ�I�P�·����(d��)��ʽ�I�P�·�Y(ji��)��(g��u)���Ρ��������㣬��Ŀǰ�@�N�Y(ji��)��(g��u)���I�P��(y��ng)��߀�dz��ձ顣ֻ���@�N�I�P�·��ÿ�����I��Ҫռ��һ��I/O�ھ����@�ӵ�Ԓ���S�����I�����ӌ�ʹI/O�ھ����㡣��ˣ��@�N�I�P�·ֻ���ڰ��I���^�ٵ���r�±��^�m�á���һ�N�I�P�·�Ǿ��ʽ�I�P�·���@�N�I�P�·�İ��I�O(sh��)�����о����о��Ľ����c(di��n)�ϣ����������I/O�ھ��Ͽ����O(sh��)�ñ��^��İ��I��ֻ���@�N�I�P�·�Y(ji��)��(g��u)�����̶����^��(f��)�s�����I�P�·�У����������cһ���c���T�·��(g��u)�Ɏ��Д���I�P�·���@�N�I�P�·�ϵ�ÿ�����I���ԆΪ�(d��)����������푑�(y��ng)�r�g�졣�@�N���Д�ʽ���I�P�·�F(xi��n)�ڑ�(y��ng)���ѽ�(j��ng)�ஔ(d��ng)?sh��)��ձ�?/strong>��D3.2��ʾ�������õ��I�P�·�Ǫ�(d��)��ʽ�I�P�·����4�������ISB1��SB4�B���քe����FPGA����ϵ�y(t��ng)��4���˿��������քe���ϸ���һ�l�Ӿ���һ��1K��������������+5V�Դ�ϡ���(d��ng)4���I���]�б�����ȥ�r������(y��ng)�ĸ��l�о�ȫ������ƽ����CMOS���T��������ÿ���˿ڵ��ƽ����ƽ������һ�����o����ȥ�r���䌦��(y��ng)��ݔ���˿��ڷ��T���������ɵ��ƽ׃?y��u)���ƽ���Ķ��������?y��ng)�Ĺ��ܡ��D3.2 �I�P�·

���I�P�·�O(sh��)Ӌ(j��)�У���Ҫ��Q���I���ӵĆ��}������(sh��)�I�P�İ��I�����ÙC(j��)е�����_�P(gu��n)��һ�����̖ͨ�^�C(j��)е�|�c(di��n)�Ĕ��_���]���^�̣���ɸߵ��ƽ���ГQ�����ڙC(j��)е�|�c(di��n)�ď������ã�һ�����I�_�P(gu��n)���]�Ϻ͔��_��˲�g��Ȼ���Sһ�B���Ķ��ӡ������ų����ӵ�Ӱ푣��ڰ��I��ݔ���˲���һ����衢һ����ݡ���D3.3��ʾ���D3.3 �V���������·

�ɈD��֪����(d��ng)�ISB1δ���r�����C�ɶ˵�늉�����1�����Tݔ����0����(d��ng)�ISB1���r������C�ɶ�늉������ܮa(ch��n)��ͻ׃���M�ܽ��|�^���п��ܳ��F(xi��n)���ӣ�ֻҪ�m��(d��ng)?sh��)��x��R��Cֵ�����ɱ��C���C�ɶ˵ķ��늉����Ӳ������^���T���_��늉���TTL��0.8V�������T��ݔ�����S�ֵ��ƽ��ͬ������(d��ng)�|�c(di��n)K���_�r���������C��(j��ng)�^R2��늣�C�ɶ˵ij��늉����Ӳ������^���T���P(gu��n)�]늉�����ˣ����T��ݔ��Ҳ������׃[9]���Ķ��_(d��)�������ӵ�Ч����

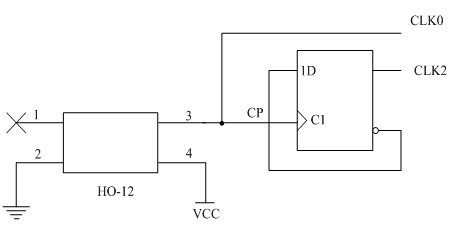

3.3 ϵ�y(t��ng)�r��·�O(sh��)Ӌ(j��)FPGA����ϵ�y(t��ng)�r��}�_�������M(j��n)�еģ���FPGA��(y��ng)��ϵ�y(t��ng)�У�Ҫ�����ʯӢ��������r��}�_����D3.4��ʾ���Dz�����ԴʯӢ����(g��u)�ɵ�ϵ�y(t��ng)�r��·����ԓ�·�У�1�_�ҿգ�2�_�ӵأ�3�_��ݔ����4�_���Դ��3�_�r��}�_ݔ�������FPGA��CLK0�r状ˣ���һ·��(j��ng)�����l�·�M(j��n)�з��l�����CLK2�r状ˡ���CLK0��CLK2�Ĺ�ͬ�����£�ϵ�y(t��ng)�M(j��n)�й�����

�r�ݔ����ϵ�y(t��ng)�·�бز����ٵ�һ���֣����ܞ�FPGA�ṩ�r��}�_��̖�����]��EDA�_�l(f��)ϵ�y(t��ng)�r�ݔ�����Ҫ�ԣ�һ����50MHz����Դ��������r���̖Դݔ�룬��Ҫ����ݔ���ĕr���̖���鲨�ΰl(f��)�����ṩ����(zh��n)�ĕr��}�_ݔ�롣

�D3.4 �r��·�D

��Դ������(q��)��������(qi��ng)�������l�ʱ��^�����_(d��)���װ���Hz��������Դ��������r�Դ����ʹ�·�ĕr犔U(ku��)��HO-12ϵ�е���Դ�������TTL/HCMOS���g(sh��)���l�ʷ�����1000Hz-1000MHz���@���҂����õ���100MHz����Դ����

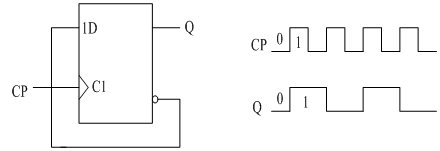

��D�|�l(f��)����ݔ��

������ݔ����cD�B�Ӿ��γ�һ�������l�·����D3.5��ʾ���IJ��ΈD���Կ���Qݔ���IJ��Ό���CP�}�_���ڵăɱ������l���Ǟ�CP�}�_��һ��[10]��

3.5 D�|�l(f��)���ӳɶ����l�·

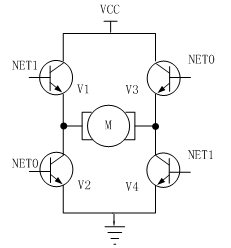

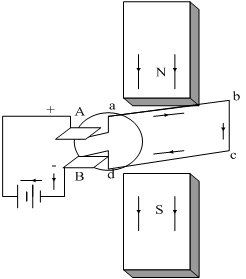

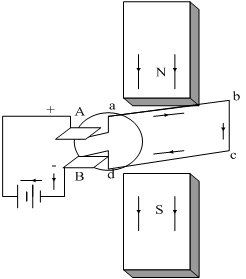

3.4 H�͘�ʽ�(q��)���·�O(sh��)Ӌ(j��)ֱ��늙C(j��)�(q��)���·ʹ����V���ľ���H��ȫ��ʽ�(q��)���·���@�N�(q��)���·���Ժܷ��㌍(sh��)�F(xi��n)ֱ��늙C(j��)���������\(y��n)�У��քe����(y��ng)���D(zhu��n)�����D(zhu��n)�Ƅӡ����D(zhu��n)�����D(zhu��n)�Ƅӡ����Ļ���ԭ��D��D3.6��ʾ���D3.6 H��ȫ��ʽ�(q��)���·

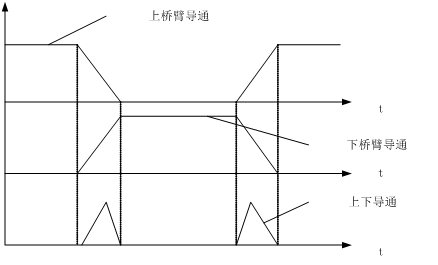

H��ȫ��ʽ�(q��)���·��4ֻ���O�ܶ������ڔز���B(t��i)��V1��V4��һ�M��V2��V3����һ�M���ɽM�Ġ�B(t��i)���a(b��)��һ�M��(d��o)ͨ�t��һ�M����P(gu��n)�ࡣ��(d��ng)V1��V4��(d��o)ͨ�r��V2��V3�P(gu��n)�࣬늙C(j��)�ɶ˼�����늉������Ԍ�(sh��) �F(xi��n)늙C(j��)�����D(zhu��n)���D(zhu��n)�Ƅӣ���(d��ng)V2��V3��(d��o)ͨ�r��V1��V4�P(gu��n)�࣬늙C(j��)�ɶ˞鷴��늉���늙C(j��)���D(zhu��n)�����D(zhu��n)�Ƅӡ���ֱ��늙C(j��)�\(y��n)�D(zhu��n)���^���У��҂�Ҫ�����ʹ늙C(j��)���Ă�����֮�g�ГQ���������D(zhu��n)�ͷ��D(zhu��n)֮�g�ГQ��Ҳ������V1��V4��(d��o)ͨ��V2��V3�P(gu��n)�࣬��V1��V4�P(gu��n)����V2��V3��(d��o)ͨ���@�ɷN��B(t��i)֮�g�D(zhu��n)�Q�����@�N��r�£���Փ��Ҫ��ɽM������̖��ȫ���a(b��)�����ǣ����ڌ�(sh��)�H���_�P(gu��n)�����������_ͨ���P(gu��n)���r�g���^���Ļ��a(b��)����߉ ��Ȼ��(d��o)�������ֱͨ��·���������Ϙ���P(gu��n)����^���У���ی�(d��o)ͨ�ˡ��@���^�̿��ÈD3.7�f�����D3.7

��ˣ����˱���ֱͨ��·�ұ��C�����_�P(gu��n)�܄���֮�g��ͬ���ԣ��ɽM������̖����Փ��Ҫ�鵹���߉�P(gu��n)ϵ������(sh��)�H�υs������һ���������^(q��)�r�g���@���C���^�̼ȿ���ͨ�^Ӳ����(sh��)�F(xi��n)����������۵ăɽM������̖֮�g�����ӕr���(q��)��������H����ͨ�^���_�P(gu��n)����ͨ������߀����ͨ�^�m(x��)�����O����ͨ����(d��ng)늙C(j��)̎���ƄӠ�B(t��i)�r��늙C(j��)�㹤���ڰl(f��)늠�B(t��i)���D(zhu��n)��������ͨ�^�m(x��)�����O����ͨ����t늙C(j��)�͕��l(f��)�ᣬ��(y��n)�ؕr�������_�P(gu��n)�ܵ��x���(q��)���·��Ӱ푺ܴ��_�P(gu��n)�ܵ��x������ѭ����ԭ�t��

��1�������(q��)���·�ǹ���ݔ����Ҫ���_�P(gu��n)��ݔ�������^��

��2���_�P(gu��n)�ܵ��_ͨ���P(gu��n)���r�g��(y��ng)�M����С

��3��ֱ��늙C(j��)ʹ�õ��Դ늉����ߣ�����_�P(gu��n)�ܵ�͉�����(y��ng)ԓ�M�����ڌ�(sh��)�H�����У��҂����x�ô����_(d��)���D��TIP122���Ч��(y��ng)��IRF530��Ч����߀���e���F(xi��n)�ڞ���ȡ�ķ��㣬�҂��x�����O�������(q��)���·���_�P(gu��n)�ܡ���ǰ��ķ�����֪��H��ȫ��ʽ�(q��)���·�У������_�P(gu��n)�����_ͨ���P(gu��n)���r�g����˴��������ֱͨ��·�Ć��}��ֱͨ��·�Ĵ��ڣ�����ʹ�_�P(gu��n)�ܰl(f��)�ᣬ��(y��n)�ؕr�����_�P(gu��n)�ܣ�ͬ�rҲ�������_�P(gu��n)�ܵ������p�ġ����ڬF(xi��n)�ڵ��S�༯���(q��)��оƬ��(n��i)���ѽ�(j��ng)��(n��i)�������^(q��)���o(h��)����LMD18200�����@����Ҫ��B���������_�P(gu��n)�ܵȷ���Ԫ���Լ��]�����^(q��)���o(h��)�ļ���оƬ�����(q��)���·�r�������^(q��)�ķ��������^(q��)�r�g�Ć��}��ֻ�������D(zhu��n)׃?y��u)鷴�D(zhu��n)���߷��D(zhu��n)׃?y��u)����D(zhu��n)�ĕr��Ŵ��ڣ��������D(zhu��n)���ӻ��D(zhu��n)���ӵĕr�]�У���˲���Ҫ����������_�P(gu��n)�ܵ��_ͨ���P(gu��n)���r�g�dz�С��������Ӳ���·�������ӕr�h(hu��n)��(ji��)�������Խ����_�P(gu��n)�ܵēp�ĺͰl(f��)�ᡣ��(d��ng)Ȼ��ͨ�^ܛ������ֱͨ��·����õ��k�������IJ������Σ������`�ͨ�^ܛ����(sh��)�F(xi��n)���^(q��)�r�g��������ͻȻ�Q��ĕr����һ���ӕr�ĭh(hu��n)��(ji��)�����_�P(gu��n)���P(gu��n)��֮�����_ͨ��(y��ng)ԓ�_ͨ���_�P(gu��n)�ܡ����_�P(gu��n)��ÿ�ΓQ��ĕr�������M(j��n)�з�����ГQ��������ʹ�_�P(gu��n)���P(gu��n)��һ�Εr�g��ʹ����ȫ�P(gu��n)����ٓQ����_������_�P(gu��n)�ܡ��@���P(gu��n)���r�g��ܛ���ӕr��(sh��)�F(xi��n)��������Ҫ������늙C(j��)��ȫ��ʽ�(q��)���·���@��ֱ��늙C(j��)�{(di��o)��ʹ�������{(di��o)�ٷ�����Ŀǰ�Ј����кܶ�N늙C(j��)�(q��)�ӵļ����·��Ч�ʸߣ��·���Σ�ʹ��Ҳ���^�V�����������(q��)�ӷ�������cȫ��ʽ�(q��)��һ�ӡ�PWM���Ʒ�����Ϙ�ʽ�(q��)���·����Ŀǰֱ��늙C(j��)�{(di��o)�����ձ�ķ�����3.5 �Դ�·�O(sh��)Ӌ(j��)����늙C(j��)�����������r���Դ�ĸɔ_�ܴ����ֻ��һ�M�Դ�r��Ӱ�ϵ�y(t��ng)�����������������҂��x���p�Դ��늡�һ�M5V�o�����·��늣� ����һ�M12V�o늙C(j��)��늡�

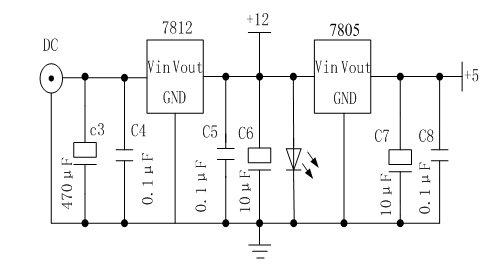

��D3.8��ʾ���Դ���ַ֞��·��һ·ֱ���ṩ12����ֱ���Դ����Ҫ���ṩ�o늙C(j��)ʹ�ã���һ·ͨ�^���˷�(w��n)��оƬ7805��(w��n)����5��ֱ���Դ�ṩ�o�I�P�·�͕r��·ʹ�ã���߅�ɂ������5���Դ�ĞV����ݣ��Gɫ��LED���鹤��ָʾ����ֻҪ�Դ�����������Gɫ��LED�͕��c(di��n)�����҂����Ը���(j��)�@��LED���Д������Դ�����Ƿ���������

3.8 �Դ�·

3.6 ��ҪԪ������������FPGA��ֱ��늙C(j��)PWM�{(di��o)��ϵ�y(t��ng)�ĺ���оƬ�x��Altera��˾FLEX10Kϵ�еĵ�EP10K10TC144-3��ԓоƬ�Ǿ��Ѓ�(n��i)���·�ߴ��С�����B���̡��ֲ����С���(q��)���·����Ĺ���С�������Ŀɾ���߉���������nj�(sh��)�(y��n)�г��õ���һ��оƬ��

FLEX10K�ǹ��I(y��)���һ��Ƕ��ʽ�Ŀɾ���߉���������ÿ��ؘ�(g��u)��CMOSSRAM��ˇ�����B�m(x��)�Ŀ���ͨ�����B�c��(d��)��Ƕ��ʽ������Y(ji��)�ϣ�ͬ�rҲ�Y(ji��)���˱���ɾ��������ă�(y��u)�c(di��n)�������ͨ�T��еĺ깦�ܡ�������(n��i)������10�f�T�·����(sh��)�F(xi��n)��(f��)�s߉�\(y��n)��͔�(sh��)��(j��)�\(y��n)�㡣EP10K10TC144-3��������FPGAоƬһ�Ӿ������µ����c(di��n)��

��1�� Ҏ(gu��)ģ�ܴ����Ƭ߉�T��(sh��)�����_(d��)����(sh��)���f������ǧ�f�T�������܌�(sh��)�F(xi��n)�Ĺ��ܺ�(qi��ng)�����Ԍ�(sh��)�F(xi��n)ϵ�y(t��ng)���ɡ��@�Ӵ���ȵp����ӡˢ�·�����e�ͽӲ���Ĕ�(sh��)�����������b����{(di��o)ԇ�M(f��i)�á�

��2�� ����ˮa(ch��n)Ʒ�Ŀɿ��ԡ���������ʽԪ��������ӡˢ�·�����b��r���������l(f��)������̓������|��������ɹ��ϣ������@�N���ϳ����y�l(f��)�F(xi��n)���o�{(di��o)ԇ�;S����ɘO������y��FPGAоƬʹ�@�N�F(xi��n)��p�٣��O(sh��)Ӌ(j��)�ˆTֻ��Ҫ���Լ��Č�(sh��)�(y��n)����Ϳ���ͨ�^���P(gu��n)��ܛӲ���h(hu��n)�������оƬ����K����ָ����

��3�� ���pС����Ӯa(ch��n)Ʒ���w�e����������������Ӯa(ch��n)Ʒ�Ĺ��ģ�����ˮa(ch��n)Ʒ�Ĺ����ٶȡ�FPGAоƬ��(n��i)���̵ܶ��B���ܴ��s�����t�r�g�����Ҳ������ⲿ�ɔ_���@������ٶȷdz�������

(4) ����ˮa(ch��n)Ʒ�ĸ���������FPGAоƬ��EPROM���ʹ�Õr���Ñ����Է���(f��)�ؾ��̡�������ʹ�û���������·���ӵ���r���ò�ͬ��EPROM�ͿɌ�(sh��)�F(xi��n)��ͬ�Ĺ��ܣ����ԣ���FPGAԇ�Ƙ�Ƭ�����������ٶ�ռ�I(l��ng)�Ј������ߣ�F(xi��n)PGAоƬ���·�O(sh��)Ӌ(j��)�����^�̣��O(sh��)Ӌ(j��)�ˆT���^�̕r�g��(n��i)������·��ݔ�롢���g����(y��u)�������棬ֱ������оƬ������

����Altera��˾��FLEX10Kϵ�о����������е����c(di��n)�����Ա��O(sh��)Ӌ(j��)�������������Ŀ��(bi��o)������ܛ�����ߞ�Altera��˾��MAX+PlusII [4]��

4 ����߉VHDL����4.1 VHDLӲ�������Z��Ӳ�������Z��HDL��EDA���g(sh��)����Ҫ�M�ɲ��֣���Ҋ��HDL�����N��

��1�� VHDL

��2�� Verilog HDL

��3�� System Verilog

��4�� System C

����VHDL��Verilog�ǬF(xi��n)��EDA�O(sh��)Ӌ(j��)��ʹ�����,Ҳ���Ў����е�����EDA���ߵ�֧�֡���System Verilog��System C�@�ɷNHDL�Z��߀̎�������^���С�VHDL������O(sh��)Ӌ(j��)����Ӳ���������Z��֮һ��VHDL��Ӣ��ȫ����VHSIC��Very High Speed Integrated Circuit��Hardware Description Language,��1983����������������DOD���l(f��)����(chu��ng)������IEEE��The Institute of Electrical Engineers���M(j��n)һ���l(f��)չ����1987�����顰IEEE��(bi��o)��(zh��n)1076����IEEE Std 1076���l(f��)�����Ĵˣ�VHDL�ɞ�Ӳ�������Z�ԵĘI(y��)���(bi��o)��(zh��n)֮һ����IEEE������VHDL�Ę�(bi��o)��(zh��n)�汾֮��EDA��˾���^�Ƴ����Լ���VHDL�O(sh��)Ӌ(j��)�h(hu��n)�����������Լ����O(sh��)Ӌ(j��)����֧��VHDL���˺�VHDL������O(sh��)Ӌ(j��)�I(l��ng)��õ��ˏV����(y��ng)�ã�����ȡ����ԭ�еķǘ�(bi��o)��(zh��n)Ӳ�������Z�ԡ�

VHDL����һ��Ҏ(gu��)���Z�Ժͽ�ģ�Z�ԣ��S��VHDL�Ę�(bi��o)��(zh��n)�������F(xi��n)��һЩ֧��ԓ�Z�Ե��О�����������ڄ�(chu��ng)��VHDL�����Ŀ��(bi��o)�����ژ�(bi��o)��(zh��n)�ęn�Ľ������·����ģ�M��������뷨������ߌ�������ϵ�y(t��ng)��Ԫ�����О顣������20���o(j��)90��������˂��l(f��)�F(xi��n)��VHDL���H��������ϵ�y(t��ng)ģ�M�Ľ�ģ���ߣ����ҿ��������·ϵ�y(t��ng)���O(sh��)Ӌ(j��)���ߣ���������ܛ�����ߌ�VHDLԴ�a�Ԅӵ��D(zhu��n)�����ı���ʽ���_(d��)�Ļ���߉Ԫ���B�ӈD�����W(w��ng)���ļ����@�N�����@Ȼ�����·�Ԅ��O(sh��)Ӌ(j��)��һ���O������M(j��n)���ܿ죬����O(sh��)Ӌ(j��)�I(l��ng)����F(xi��n)�˵�һ��ܛ���O(sh��)Ӌ(j��)���ߣ���VHDL߉�C���������ј�(bi��o)��(zh��n)VHDL�IJ����Z�������D(zhu��n)������w�·��(sh��)�F(xi��n)�ľW(w��ng)���ļ���

VHDL�Z�Ծ��к�(qi��ng)���·�����ͽ�ģ�������Ķ����ӴΌ���(sh��)��ϵ�y(t��ng)�M(j��n)�н�ģ���������Ķ������Ӳ���O(sh��)Ӌ(j��)�΄�(w��)��������O(sh��)Ӌ(j��)Ч�ʺͿɿ��ԡ�

VHDL�����c���wӲ���·�o�P(gu��n)���c�O(sh��)Ӌ(j��)ƽ�_�o�P(gu��n)�����ԣ����Ҿ������õ��·�О�������ϵ�y(t��ng)���������������Z�����x�Ժ͌Ӵλ��Y(ji��)��(g��u)���O(sh��)Ӌ(j��)������F(xi��n)�ˏ�(qi��ng)����������͑�(y��ng)�Ý�������ˣ�VHDL֧�ָ��Nģʽ���O(sh��)Ӌ(j��)��������������c�Ե����ϻ��Ϸ��������挦��(d��ng)���S����Ӯa(ch��n)Ʒ�������ڿs�̣���Ҫ��������O(sh��)Ӌ(j��)���������¼��g(sh��)����׃��ˇ�ȷ���,VHDL�������õ��m��(y��ng)��,��VHDL�M(j��n)�����ϵ�y(t��ng)�O(sh��)Ӌ(j��)��һ���ܴ�ă�(y��u)�c(di��n)���O(sh��)Ӌ(j��)�߿��Ԍ�����־���书�ܵČ�(sh��)�F(xi��n),������Ҫ����Ӱ푹��ܵ��c��ˇ���P(gu��n)�����ػ��M(f��i)�^��ĕr�g�;�����

���g(sh��)���w�ٰl(f��)չʹ�ü����·���O(sh��)Ӌ(j��)Ҏ(gu��)ģ��������(f��)�s�̶��������ߡ����S���O(sh��)Ӌ(j��)Ҏ(gu��)ģ�������y(t��ng)���������ϵġ�����ͨ��߉Ԫ������Ӳ����������׃���^�ڏ�(f��)�s��������ʹ�á��S����Ҏ(gu��)ģ���ü����·(ASIC)���_�l(f��)�����ƣ���������_�l(f��)��Ч�ʣ����Ӽ����_�l(f��)�ɹ����^�����Լ��s���_�l(f��)�r�g����ASIC���ƺ����a(ch��n)�S�����^�_�l(f��)�����ڸ���Ŀ��Ӳ�������Z��(HDL)����������Ӳ���·�Ĺ��ܣ���̖�B���P(gu��n)ϵ�����r�P(gu��n)ϵ���Z�ԣ����ܱ�ԭ��D����Ч�ر�ʾӲ���·������[5]��

VHDL�Z�Ծ����������c(di��n):

��1��VHDL�Z�Կ���֧����������(Top Down)�ͻ��ڎ�(Library-Based)���O(sh��)Ӌ(j��)����������߀֧��ͬ���·�������·�������S�C(j��)�·���O(sh��)Ӌ(j��)���䷶��֮�Vʹ����HDL�Z�������ܱȔM�ġ�

��2��VHDL�Z�Ծ��ж��Ӵ�����ϵ�y(t��ng)Ӳ�����ܵ����������ԏ�ϵ�y(t��ng)�Ĕ�(sh��)�W(xu��)ģ��ֱ���T���·:֧�ִ�Ҏ(gu��)ģ�O(sh��)Ӌ(j��)�ķֽ���O(sh��)Ӌ(j��)����;֧�ւ�ݔ���t�͑T�����t�����Ը���(zh��n)�_�Ľ�����(f��)�s���·Ӳ��ģ�͡�

��3������VHDL�Z���O(sh��)Ӌ(j��)ϵ�y(t��ng)Ӳ���r���]��Ƕ���c��ˇ���P(gu��n)����Ϣ���@���ڹ�ˇ���r���͟o����ԭ�O(sh��)Ӌ(j��)����ֻҪ��׃����(y��ng)��ӳ�乤���ɡ���Ҋ���oՓ���·߀���Ĺ�ˇ���֮�g�����a(ch��n)��ʲô����Ӱ푡�

��4��VHDL�Z�Լ�����һ�NIEEE�Ĺ��I(y��)��(bi��o)��(zh��n)���O(sh��)Ӌ(j��)�ɹ����ڏ�(f��)�úͽ������@�����M(j��n)һ���Ƅ�VHDL�Z�Ե��ƏV������:���⣬VHDL�Z�Ե��Z�����^��(y��n)�o��x��ʹ�ö������˘O��ĺ�̎��

��5��VHDL�Z�Ծ��в��l(f��)�ԣ��w�F(xi��n)�ڃɂ����棺����ʹ��VHDL�Z���M(j��n)�Д�(sh��)���·�O(sh��)Ӌ(j��)�r���ڲ��l(f��)�ԣ���VHDL�Z��֧���O(sh��)Ӌ(j��)�ֽ⣬��ʹ���ֽ�ĸ��Ӳ��ֵ��O(sh��)Ӌ(j��)������ɣ��@Щ�Ӳ��ֵ��O(sh��)Ӌ(j��)�������ֽM�ɣ����x��(sh��)�w���_��ģ���c�h(hu��n)���Ľӿڣ����x�Y(ji��)��(g��u)�w�����ģ�͵Ĺ������������x�yԇ���֡���ģ�����ɜyԇ�����������@ģ��ݔ����̖��B(t��i)�Թ���������Σ�VHDL�Z���ڈ�(zh��)���Ͼ��в��l(f��)�ԣ����m�������·�IJ��l(f��)�����c(di��n)[4]��

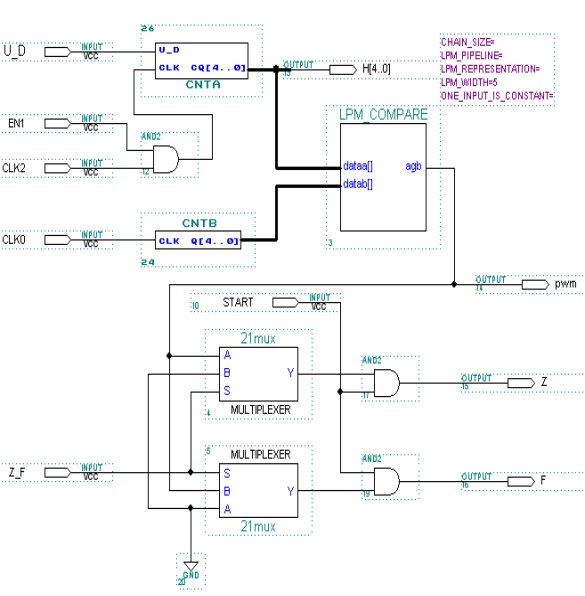

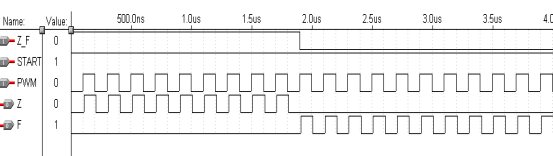

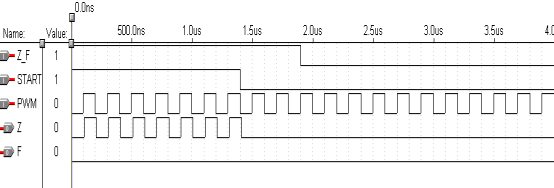

4.2 FPGA��(n��i)��߉�M���D4.1 FPGAֱ��늙C(j��)PWM �����·

�ɈD4.1���Կ���늙C(j��)����߉ģ�K��PWM�}���{(di��o)����̖�a(ch��n)���·����������·�M�ɡ�����PWM�}���{(di��o)����̖�a(ch��n)���·�ɿɿصļӜpӋ(j��)��(sh��)��CNTA��5λ���M(j��n)��Ӌ(j��)��(sh��)��CNTB����(sh��)�ֱ��^��LPM_COMPARE�����ֽM�ɣ���������·�Ƀɂ����xһ�·21MUX�M�ɡ��B����ÿ��ģ�K�Ķ˿ڵ�������2.5���ѽ�(j��ng)Ԕ��(x��)���f�������@��Ͳ����؏�(f��)�������͌�PWM�}���{(di��o)����̖�a(ch��n)���·��VHDL�����c���桢�����·��VHDL�����c�����M(j��n)��Ԕ��(x��)�ķ�����

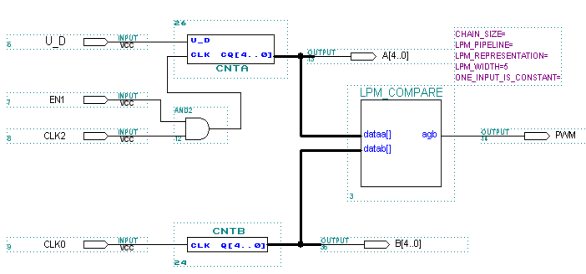

4.3 PWM�}���{(di��o)����̖�a(ch��n)���·����PWM�}���{(di��o)����̖�a(ch��n)���·�ɿɿصļӜpӋ(j��)��(sh��)��CNTA��5λ���M(j��n)��Ӌ(j��)��(sh��)��CNTB����(sh��)�ֱ��^��LPM_COMPARE�����ֽM�ɡ��ɿصļӜpӋ(j��)��(sh��)������(x��)��Ӌ(j��)��(sh��)�����_���}�_���ȡ���(d��ng)U/D=1�r��ݔ��CLK2,ʹ�O(sh��)��ֵӋ(j��)��(sh��)����ݔ��ֵ���ӣ�PWM��ռ�ձ�����,늙C(j��)�D(zhu��n)�ټӿ죻��(d��ng)U/D =0��ݔ��CLK2,ʹ�O(sh��)��ֵӋ(j��)��(sh��)����ݔ��ֵ�pС,PWM��ռ�ձȜpС��늙C(j��)�D(zhu��n)��׃����5λ���M(j��n)��Ӌ(j��)��(sh��)����CLK0��������,��X��Ӌ(j��)��(sh��)��ݔ�������Ծ������ӵ���X������(d��ng)Ӌ(j��)��(sh��)ֵС���O(sh��)��ֵ�r����(sh��)�ֱ��^��ݔ�����ƽ����(d��ng)Ӌ(j��)��(sh��)ֵ�����O(sh��)��ֵ�r,��(sh��)�ֱ��^��ݔ�����ƽ���ɴˮa(ch��n)�������Ե�PWM���Ρ����(n��i)��߉�D��D4.2��ʾ��

�D 4.2 FPGA�е�PWM�}���{(di��o)����̖�a(ch��n)���·

�ɿصļӜpӋ(j��)��(sh��)��CNTA�еĶ˿�U_D����Ӌ(j��)��(sh��)���ķ���EN1��Ӌ(j��)��(sh��)����ʹ�ܶˣ�����Ӌ(j��)��(sh��)����ֵ��׃����U_D=1�r���ӜpӋ(j��)��(sh��)��CNTA���}�_CLK2�������£�ÿ��һ���}�_��Ӌ(j��)��(sh��)��CNTA��1��U_D=0�r��ÿ��һ���}�_��Ӌ(j��)��(sh��)��CNTA�p1��ʹ�ܶ�EN1�O(sh��)��Ӌ(j��)��(sh��)��ֵ�ij�ֵ����(d��ng)EN1��1׃?y��u)?�ĕr�oՓU_D��α�����Ӌ(j��)��(sh��)����ֵ�������l(f��)��׃�����@�Ӿ������Ӌ(j��)��(sh��)�����O(sh��)��ֵ������沨����D4.3��ʾ����VHDL�Z�����¡�

LIBRARY IEEE;

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CNTA IS

PORT(CLK:IN STD_LOGIC;

U_D:IN STD_LOGIC;

CQ:OUT STD_LOGIC_VECTOR(4 DOWNTO 0));

END CNTA;

ARCHITECTURE behav OF CNTA IS

SIGNAL CQI:STD_LOGIC_VECTOR(4 DOWNTO 0);

BEGIN

PROCESS(CLK)

BEGIN

IF CLK'EVENT AND CLK='1'THEN

IF U_D='1' THEN

IF CQI<=31 THEN CQI<="11111";

ELSE CQI<=CQI+1; END IF;

ELSIF CQI=0 THEN CQI<="00000";

ELSE CQI<=CQI-1;END IF;

END IF;

END PROCESS;

CQ<=CQI;

END behav;

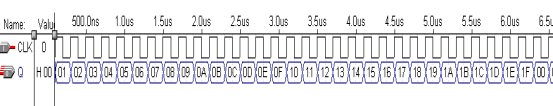

�D 4.3 ��(x��)��Ӌ(j��)��(sh��)���ķ��沨��

CNTB��һ�����ε�5λ���M(j��n)��Ӌ(j��)��(sh��)�������Ĺ���ԭ����CNTA��ԭ�������ƣ��҂�ֻ����CNTA�ĕr状˼���һ��ʹ�ܶ�EN1������Ӝp�ķ���CNTB�ĕr状˛]�м�ʹ�ܶˣ�����ÿ��һ���}�_Ӌ(j��)��(sh��)����1����?y��n)�CNTB��һ��5λ�Ķ��M(j��n)ֵӋ(j��)��(sh��)�������Ԯ�(d��ng)Ӌ(j��)��(sh��)����ֵ��(d��ng)����32�r��Ӌ(j��)��(sh��)��������0�_ʼӛ��(sh��)���Ķ��a(ch��n)�������Եľ������ӵ���X��������沨����4.4����VHDL�Z�����¡�

ENTITY CNTB IS

PORT(CLK: IN BIT;

Q:BUFFER INTEGER RANGE 31 DOWNTO 0);

END;

ARCHITECTURE BHV OF CNTB IS

BEGIN

PROCESS(CLK)

BEGIN

IF CLK'EVENT AND CLK='1' THEN

Q<=Q+1;

END IF;

END PROCESS;

END BHV;

�D4.4 5λ���M(j��n)��Ӌ(j��)��(sh��)�����沨��

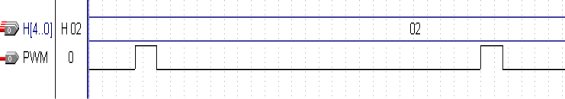

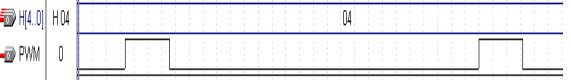

��(sh��)�ֱ��^���Ǯa(ch��n)��PWM���εĺ��ĽM�ɲ������ɿصļӜpӋ(j��)��(sh��)��CNTA��5λ���M(j��n)��Ӌ(j��)��(sh��)��CNTBͬ�r�Ӕ�(sh��)�ֱ��^��LPM-COMPARE�ɶ������·ݔ����̖����(d��ng)Ӌ(j��)��(sh��)��CNTBݔ��ֵС�ڼ�(x��)��Ӌ(j��)��(sh��)��CNTAݔ����Ҏ(gu��)��ֵ�r, ���^��ݔ�����ƽ; ��(d��ng)CNTBݔ��ֵ���ڼ�(x��)��Ӌ(j��)��(sh��)��CNTAݔ����Ҏ(gu��)��ֵ�r, ���^��ݔ�����ƽ����׃��(x��)��Ӌ(j��)��(sh��)�����O(sh��)��ֵ, �Ϳ��Ը�׃PWMݔ����̖��ռ�ձȡ����˱����^����沨�Σ�����CNTB��ݔ������B[4..0]�����沨����D4.5��

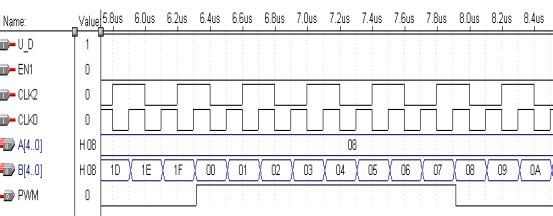

�D4.5 ��(sh��)�ֱ��^���ķ��沨��

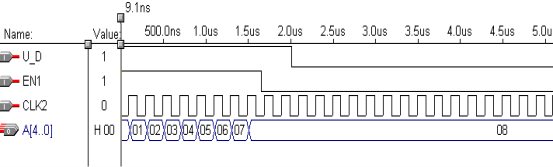

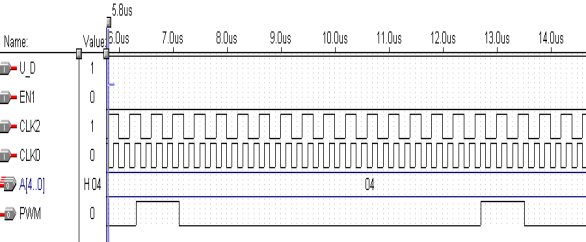

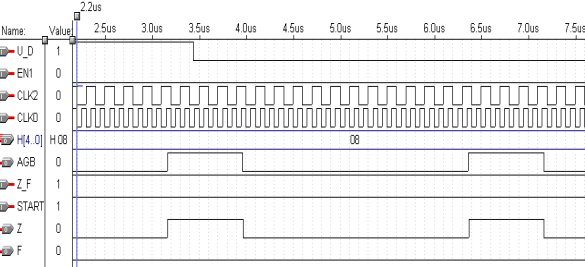

��(x��)��Ӌ(j��)��(sh��)��CNTA��һ���p��Ӌ(j��)��(sh��)��, �����M(j��n)�мӜpӋ(j��)��(sh��),��U_D�������/�pӋ(j��)��(sh��)����, CLK��Ӌ(j��)��(sh��)�r�ݔ��ˡ����˱����B�m(x��)׃�ٿ���, ��Ӌ(j��)��(sh��)����CLK��ͨ�^���c���T, ������CLK2�ⲿ׃�ٿ��Ƹ��ӕr�, ����EN1��̖�����Ƿ����S׃�١��ڱ����O(sh��)Ӌ(j��)��ֱ��늙C(j��)�D(zhu��n)���M(j��n)����32����(x��)�֡�����沨����D4.6����(x��)��Ӌ(j��)��(sh��)���ij�ֵ���O(sh��)��08H��Ҳ����ʮ�M(j��n)ֵ��8����(d��ng)Ӌ(j��)��(sh��)��CNTB��ֵС��8�r��AGBݔ�����ƽ����(d��ng)Ӌ(j��)��(sh��)��CNTB��ֵ����8�r��AGB��ݔ��ֵ����ƽ���Ķ��a(ch��n)��PWM���Ρ�

�D4.6 A[4..0]=08H�r늙C(j��)����PWM����

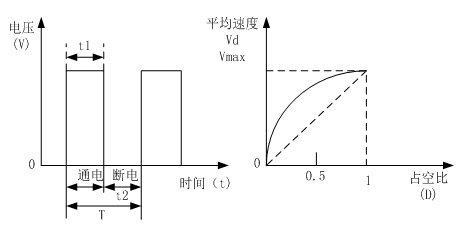

ͨ�^��׃��(x��)��Ӌ(j��)��(sh��)����ֵ�Ϳ��Ը�׃PWM��ռ�ձȣ��Ķ���׃ֱ��늙C(j��)���ٶȡ��ڈD4.6��ռ�ձ�D=8/32=0.25���ڈD4.7��ռ�ձ�D=4/32=0.125��ͨ�^���σɽM��(sh��)��(j��)���^�Լ��������沨���҂����Կ�����ֻҪ��׃ʹ�ܶ��ƽ�ĸߵͣ�����Ը�׃��(x��)��Ӌ(j��)��(sh��)����ֵ��Ҳ���Ǹ�׃��(x��)��Ӌ(j��)��(sh��)��CNTA�ij�ֵ���Ķ����Ը�׃ֱ��늙C(j��)��ռ�ձȣ���׃ֱ��늙C(j��)���ٶȡ�

�D4.7 A[4..0]=04H�r늙C(j��)�p��PWM����

�{(di��o)��(ji��)PWM����ռ�ձ���늙C(j��)�{(di��o)�ٵ���Ҫ�ֶΣ����}��Ӌ(j��)��(sh��)��CNTA��ֵ��u����ݔ���}�_���_���r�g׃��PWMռ�ձ���u׃��������ݔ���o늙C(j��)늘е��������ӣ�늙C(j��)���١����}��Ӌ(j��)��(sh��)�����r��CNTA��ֵ�pС��ݔ���}�_���_���r�g׃С��PWMռ�ձ���u׃С����������ݔ���o늙C(j��)늘е������p�٣�늙C(j��)�p�١���(d��ng)늙C(j��)�õ�������̖��ռ�ձ������������{(di��o)���������ֵ�֣�늙C(j��)�õ��p����̖��ռ�ձȜpС�����Ŀ��{(di��o)��������Сֵ�֡�

4.4 �\(y��n)������߉�·������D4.8��ʾFPGA�еĹ���/ֹͣ���ƺ���/���D(zhu��n)��������·����ɂ����xһ��·�x�������σɂ��c�T����(j��)߉ԭ���M�϶��ɡ�START�Iͨ�^���c���T����PWMݔ��,��(sh��)�F(xi��n)��늙C(j��)�Ĺ���/ֹͣ���ơ���(d��ng)START�˽Ӹ��ƽ�r����ʾ�Դ��ͨ��늙C(j��)�_ʼ�\(y��n)�D(zhu��n)����(d��ng)START�˽ӵ��ƽ�r��늙C(j��)ֹͣ�\(y��n)�D(zhu��n)��Z/F�I�����x��PWM�����Ǐ�����Z�M(j��n)��H��߀�Ǐ�ؓ(f��)��F�M(j��n)��H���Կ���늙C(j��)�����D(zhu��n)����(d��ng)Z/F=1�rPWMݔ�����Ώ�����Z�M(j��n)��H��늙C(j��)���D(zhu��n)����(d��ng) Z/F =0�rPWMݔ�����Ώ�ؓ(f��)��F�M(j��n)��H��늙C(j��)���D(zhu��n)��������D4.9��ʾ��

�D4.8 FPGA�еĹ���/ֹͣ���ƺ���/���D(zhu��n)��������·

�D4.9 ��/���D(zhu��n)���������·����

��(d��ng)START=1�r���c�T���_�����S늙C(j��)��������(d��ng)START=0�r���c�T�P(gu��n)�]��늙C(j��)ֹͣ�D(zhu��n)�ӡ�������D4.10��ʾ��

�D4.10������/ֹͣ�·����

5 ֱ��늙C(j��)PWM�{(di��o)��ϵ�y(t��ng)����

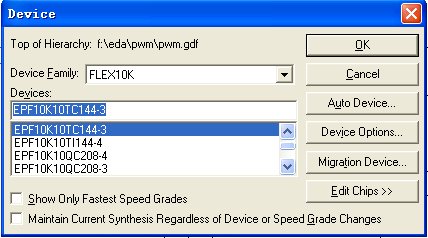

5.1 FPGA�_�l(f��)�h(hu��n)���Ľ�BMAX+Plus II(MuliPtle Array Martix and Programmxnaable Logie User System)��ALTERA��˾�Ƴ��ľ�����ȫ���ɻ�����ҕ�����O(sh��)Ӌ(j��)�h(hu��n)�������й��I(y��)��(bi��o)��(zh��n)EDA���߽ӿڣ����\(y��n)���ڶ�N����ϵ�y(t��ng)��MAX+Plus II�ṩ��һ�N�c�Y(ji��)��(g��u)�o�P(gu��n)���O(sh��)Ӌ(j��)�h(hu��n)�����O(sh��)Ӌ(j��)�ˆT�o횾�ͨ������(n��i)���Y(ji��)��(g��u)��ֻ���\(y��n)���Լ���Ϥ��ݔ�빤���M(j��n)���O(sh��)Ӌ(j��)���Ϳ���ͨ�^MAX+Plus II���@Щ�O(sh��)Ӌ(j��)�D(zhu��n)�Q����K�Y(ji��)��(g��u)����Ҫ�ĸ�ʽ��

MAX+Plus II�ṩ�S����߉���ܹ��O(sh��)Ӌ(j��)�ˆT�{(di��o)�ã����а���74ϵ��ȫ�������ĵ�Ч�깦��Ͷ�N����ĺ깦��(MacorFunctino)ģ�K�Լ�����(sh��)���ĺ깦��(Mageufnctino)ģ�K��MAX+PlusH߀�����_�ź˵����c(di��n)�����S�O(sh��)Ӌ(j��)�ˆT�����Լ��ĺ깦��ģ�K����������@Щ߉����ģ�K�����Դ��p�p�O(sh��)Ӌ(j��)�Ĺ��������ɱ��s���_�l(f��)���ڡ�

Altera��˾��MAX+plus II���������c(di��n)��

�_�ŵĽ��桪��MAX+plus IIܛ�����c�������I(y��)��(bi��o)��(zh��n)���O(sh��)Ӌ(j��)ݔ�롢�C���cУ�(y��n)�������B�ӣ�֧���cCandence��Synopsys��Viewlogic��������˾���ṩ��EDA�ӿڡ�

��ȫ���ɻ�����MAX+plus II���O(sh��)Ӌ(j��)ݔ�롢̎���cУ�(y��n)����ȫ�������ڽy(t��ng)һ���_�l(f��)�h(hu��n)���£��@�ӿ��Լӿ�ӑB(t��i)�{(di��o)ԇ���s���_�l(f��)���ڡ�

�S�����O(sh��)Ӌ(j��)�졪��MAX+plus II�ṩ�S���Ď��Ԫ���O(sh��)Ӌ(j��)���{(di��o)�ã����а���74ϵ�е�ȫ�������������Ĕ�(sh��)�����������ͅ���(sh��)���ĺ꺯��(sh��)�����p�p���O(sh��)Ӌ(j��)�ˆT�Ĺ�������

Ӳ�������Z�ԡ���MAX+plus IIܛ��֧�ָ��NHDL�O(sh��)Ӌ(j��)ݔ���x�(xi��ng)������VHDL��verilog HDL��Altera��˾�Լ���Ӳ�������Z��AHDL��

�_�ź����ԡ���MAX+plus IIܛ�������_�ź˵����c(di��n)�������S�O(sh��)Ӌ(j��)�ˆT�����Լ��J(r��n)���Ѓr(ji��)ֵ�ĺ꺯��(sh��)��

MAX+plus IIܛ�����O(sh��)Ӌ(j��)ݔ�뷽���ж�N����Ҫ����ԭ��Dݔ�뷽ʽ���ı��O(sh��)Ӌ(j��)ݔ�뷽ʽ�������O(sh��)Ӌ(j��)ݔ�뷽ʽ�ȡ�

(1) ԭ��Dݔ���c��̖��������MAX+plus II�ṩ�ĸ��Nԭ��D���M(j��n)���O(sh��)Ӌ(j��)ݔ����һ�N���ֱ�ӵ�ݔ�뷽ʽ�����@�N��ʽݔ��r�������Ч�ʣ���(y��ng)�����������߉�։K���Ѵ�Ҏ(gu��)ģ���·���ֳ�����С�K�ķ�����

(2) Ӳ�������Z��ݔ�롣MAX+plus II����һ�����ɵ�Text Editor(�ı�������)���m����ݔ��;���VHDL�Z�Ծ������O(sh��)Ӌ(j��)�ļ���

(3) MAX+plus II Waveform Editor(���ξ�����)���ڽ����;������ļ���ݔ������������ܜyԇ�������m���ڕr����؏�(f��)�ĺ���(sh��)��

�O(sh��)Ӌ(j��)�ˆT���Ը���(j��)�Լ��Č�(sh��)�H��r�`����x��MAX+plus IIܛ����ݔ�뷽ʽ����ϵ�y(t��ng)�M(j��n)�Д�(sh��)�W(xu��)��������Ҫ����VHDL�Z�Ե��О��������ڔ�(sh��)�W(xu��)ģ�ͽ���֮����Ҫ�Ğ锵(sh��)��(j��)��������ʽ�����@���^���У��������ɷN��r:һ�N�nj��r�gҪ���^�ߵIJ��ּ��r��߉����һ�N�Ǡ�B(t��i)�C(j��)���M��߉�����ڕr��߉����VHDL�Z�ԵĔ�(sh��)��(j��)�������ķ�ʽҪ�õ������Ļ�����(sh��)�����������T�·���|�l(f��)���ȣ��@Щ������ʹ��Ҫ�õ�VHDL�Z�Ե�Ԫ�������Z���Ԫ�������Z�䣬����߀Ҫ���x���������g׃������Ԫ����ݔ��ݔ�������������Ƿdz����㡣�@�N��r��ʹ��ԭ��Dݔ���Ƿdz�ֱ�^�ͷ���ġ���B(t��i)�C(j��)(Sate Machine)��һ�Nӛ��½o���r�̠�B(t��i)���O(sh��)�䣬������(j��)ݔ�댦ÿ���o����B(t��i)�ĸ�׃����׃���B(t��i)�����l(f��)һ����������B(t��i)�C(j��)�ǿ����·�O(sh��)Ӌ(j��)�е���Ҫ���֣����Ĺ���ʮ�֏�(qi��ng)��Ҏ(gu��)�����¼��ĺϷ���B(t��i)���D(zhu��n)�Q�l��������̖�Зl��Ҫ��Ĉ��Ϸdz��m�á��@�ӵ���r��ԭ��D�DZ��^�y�Ա����ģ�����VHDL�Z�Ԅt�ܺ��Σ���������(y��ng)���x���Z�伴�ɡ����������Ġ�B(t��i)�C(j��)��������һ���µĺ꺯��(sh��)��ԭ��D�{(di��o)�á�

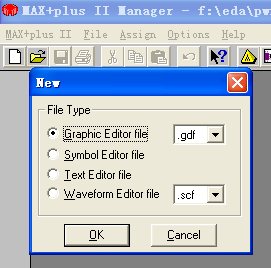

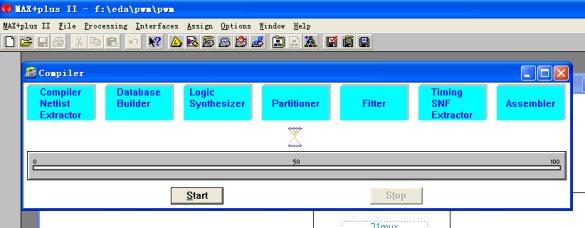

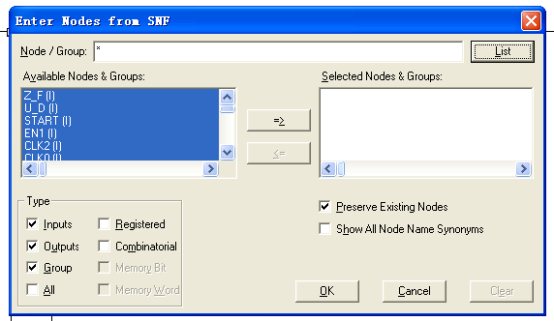

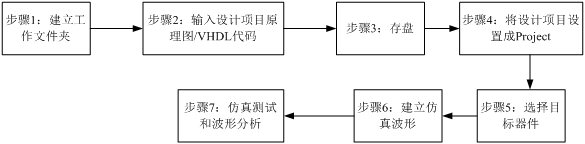

5.2 ���������(xi��ng)Ŀ�ڱ����O(sh��)Ӌ(j��)�У���Ҫ�õ����O(sh��)Ӌ(j��)������ԭ��Dݔ���O(sh��)Ӌ(j��)��MAX+plus II�ṩ�˹���(qi��ng)��ֱ�^��ݺͲ����`���ԭ��Dݔ���O(sh��)Ӌ(j��)���ܣ�ͬ�r߀������m���ڸ��N��Ҫ��Ԫ���죬���а�������߉Ԫ���죨���c���T����������D�|�l(f��)���ȣ����깦��Ԫ���������ˎ�����74ϵ�е����������Լ�����(qi��ng)���������õ������IP Core�ľ��܉KLPM�졣��������Ҫ���ǣ�MAX+plus II߀�ṩ��ԭ��Dݔ����Ӵ��O(sh��)Ӌ(j��)���ܣ�ʹ���Ñ����O(sh��)Ӌ(j��)����Ҏ(gu��)ģ���·ϵ�y(t��ng)���Լ�ʹ�÷��㾫�����õĕr���������ͨ�^�r����棬�܌�Ѹ�ٶ�λ�·ϵ�y(t��ng)���e�`���ڣ����S�r�m���� �܌��O(sh��)Ӌ(j��)�������S�r���ģ��������O(sh��)Ӌ(j��)�^�������е��·�͜yԇ�ļ������������κ������p�ĺ͓p�ģ����ϬF(xi��n)������O(sh��)Ӌ(j��)���g(sh��)Ҏ(gu��)���������B�����O(sh��)Ӌ(j��)���E��

��1���鹤���O(sh��)Ӌ(j��)����һ���ļ��A�������O(sh��)Ӌ(j��)���ļ�ȡ����eda,·����F:\eda��

��2��ݔ���O(sh��)Ӌ(j��)�(xi��ng)Ŀ�ʹ�P

�ٴ��_MAX+Plus II���x�ˆ�File�е�new���ڏ����Č�Ԓ�����x��ԭ��D��ݔ���(xi��ng)��Graphic Editor File�� ��D5.1��ʾ������OK���I����_ԭ��D���ڡ�

�D5.1 ����ԭ��D������Ԓ��

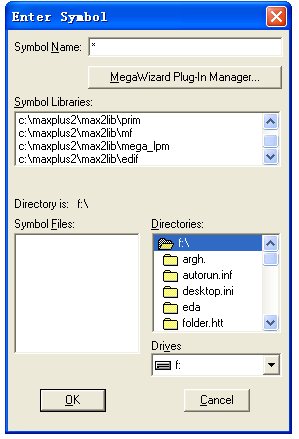

��Ȼ���ھ����ڵ���һλ�����ғ���������һ���ˆΣ��x�����е�ݔ��Ԫ���(xi��ng)��Enter Symbol�������nj�������D5.2��ʾ��Ԫ��ݔ�댦Ԓ��

�D5.2 Ԫ��ݔ�댦Ԓ��

����Symbol Name��ݔ�뱾�O(sh��)Ӌ(j��)��Ҫ�õ���Ԫ��������xһ��·�x����21 MUX����(sh��)�ֱ��^��LPM_COMPARE�ȵȣ��نΓ�OK���o������Ԍ�Ԫ���{(di��o)��ԭ��D�������С�

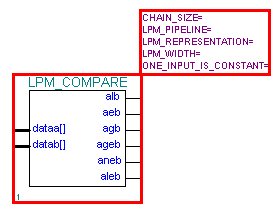

ע�⣺�ڱ����O(sh��)Ӌ(j��)����Ҫ�õ���VHDL�Z������������CNTA��CNTB�ɂ���B(t��i)�C(j��)�����µĺ꺯��(sh��)��ԭ��D�{(di��o)�á�߀Ҫ�õ�һ������(sh��)���{(di��o)�ĺ꺯��(sh��)LPM_COMPARE������w�IJ����������ڈD5.2ԭ��D������ݔ��LPM_COMPARE���Γ���OK���I��������ҵ�LPM_COMPARE����D5.3��ʾ��

�D5.3 ����(sh��)δ�O(sh��)�õĔ�(sh��)�ֱ��^���D��(bi��o)

�p��D5.3�е�LPM_COMPARE���Ͻǵą���(sh��)�@ʾ���֣�Ȼ���ڏ����ą���(sh��)�O(sh��)�Ì�Ԓ�����x����m�ą���(sh��)����D5.4��ʾ��

�D5.4 ����(sh��)�O(sh��)�Ì�Ԓ��

��(sh��)�ֱ��^�����˿ڼ��䅢��(sh��)�ĺ��x�ǣ�

Aclr����������ݔ�룻

Alb��aAeb��,agb��ageb��,aneb��aleb�����^����(sh��)��(j��)ݔ����

Clock���������|�l(f��)ӛ��(sh��)�r�ݔ�룻

Dataa[]�����Д�(sh��)��(j��)ݔ��ˣ�

�O(sh��)����r��D4.1��ʾ�����^��λ����5����5λ���^��

���x��ˆ�File�е�Save as,�x���Ĺ����(xi��ng)ĿF:\eda�����O(sh��)Ӌ(j��)�õĈD���ļ�ȡ���飺PWM.gdf,����P���@��Ŀ��С�

(3) ���O(sh��)Ӌ(j��)�(xi��ng)Ŀ�O(sh��)�óɹ����ļ�

����ʹMAX+plus II�܌�ݔ����O(sh��)Ӌ(j��)�(xi��ng)Ŀ���O(sh��)Ӌ(j��)�ߵ�Ҫ���M(j��n)�и��(xi��ng)̎������회�PWM.gdf�O(sh��)�ó�Project��

�D5.5���O(sh��)Ӌ(j��)�(xi��ng)Ŀ�O(sh��)�óɹ����ļ�

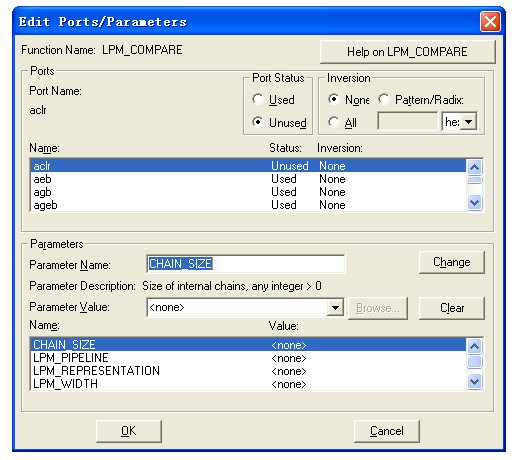

(4)�x��Ŀ��(bi��o)���������g

���˫@���cĿ��(bi��o)����������(y��ng)�ġ����_�ĕr������ļ����ڌ��ļ����gǰ����x����(sh��)�F(xi��n)���(xi��ng)Ŀ��Ŀ��(bi��o)�������ڱ����O(sh��)Ӌ(j��)���x��EPF10K10TC144-3����Ӿ��g��

�D5.6 �x��Ŀ��(bi��o)����

�D5.7 ���ļ��M(j��n)�о��g���C�Ϻ��m��Ȳ���

(5) �r�����

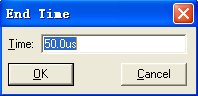

�r��������Ҫ��(n��i)���ǽ��������ļ�(�ͽ���ԭ��Dݔ���O(sh��)Ӌ(j��)һ��)��ݔ����̖��(ji��)�c(di��n)���O(sh��)�ò��΅������O(sh��)������r�g�������ļ���P���\(y��n)�з���ͷ�������[5]��

5.8 ݔ����̖��(ji��)�c(di��n)

5.9 �O(sh��)������r�g

����Ԕ��(x��)��B��B��ԭ��D���O(sh��)Ӌ(j��)���̣��F(xi��n)�ڌ���w�{���£�

5.10 �(xi��ng)Ŀݔ���O(sh��)Ӌ(j��)��D

�ڱ����O(sh��)Ӌ(j��)�У���Ҫ�M��ļ��g(sh��)Ҫ�����O(sh��)Ӌ(j��)������/���D(zhu��n)����/ͣ���ƹ��ܡ��ٶ��ھ����{(di��o)��ֱ��늙C(j��)�����b�á��������÷��沨��Ԕ��(x��)���f�������O(sh��)Ӌ(j��)���·�M�����ϵ�����Ҫ��

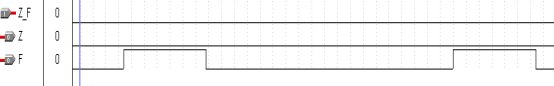

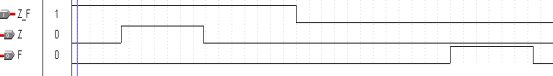

5.3 ��/���D(zhu��n)���������I�PZ_F��늙C(j��)�ķ�������I����(d��ng)Ҫ��늙C(j��)���D(zhu��n)�r��ֻ��Ҫ�����IZ_F����ʾZ_Fݔ�����ƽ����Z_F=1��늙C(j��)���D(zhu��n)����D5.11��ʾ����(d��ng)�IZ_F���_�r��Z_F��0�r��늙C(j��)���D(zhu��n)����D5.12���D5.13��ʾ��

�D5.11 늙C(j��)���D(zhu��n)

5.12 늙C(j��)���D(zhu��n)

�D5.13 늙C(j��)�����D(zhu��n)

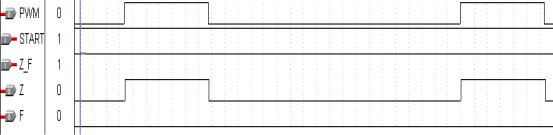

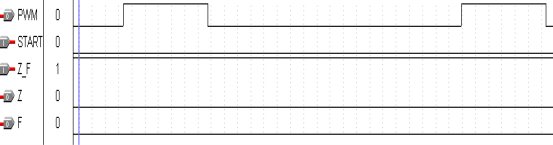

5.4 ��/ͣ��������START�I��늙C(j��)�Ć����I����(d��ng)����START�I�r��START=1,늙C(j��)�M(j��n)���\(y��n)�Р�B(t��i)����D5.14��ʾ����֮��START=0�r��늙C(j��)ֹͣ����D5.15���D5.16��ʾ��

�D5.14 ���ӷ��沨��

�D5.15 ֹͣ���沨��

�D5.16 ��/ͣ���沨��

5.5 ��/�p�������I�PEN1����늙C(j��)�Ƿ����S׃�١�����ͨ�^��׃EN1����Ը�׃�O(sh��)��ֵH[4..0]��ֵ��Ҳ�����O(sh��)��ֵ�ij�ֵ���Ķ���׃��ֱ��늙C(j��)��ռ�ձȣ���׃ֱ��늙C(j��)���ٶȣ��_(d��)���{(di��o)�ٵ�Ŀ�ġ�

��?y��n)�CNTB��5λ��Ӌ(j��)��(sh��)�������ڱ��O(sh��)Ӌ(j��)��ֱ��늙C(j��)�D(zhu��n)�ټ�(x��)�֞�32������D5.17��ռ�ձȞ�2/32=0.0625��ͬ��ͨ�^���IEN1ԓ׃H[4..0]��ֵ��õ���D5.18��5.19��PWM���沨�Σ���ռ�ձ����Ξ�0.125��0.25��Ҳ����ռ�ձ�����늙C(j��)���ٶ����ӡ�����(j��)���ϵĔ�(sh��)��(j��)���^�c���沨�εķ������Կ�����늙C(j��)���ٶ�����u�����ӡ�����ͨ�^��׃EN1��ֵ���Ը�׃ֱ��늙C(j��)��PWMռ�ձȣ��Ķ���׃ֱ��늙C(j��)���ٶȡ�

�D5.17 H[4..0]=02H���沨��

�D5.18 H[4..0]=04H���沨��

�D5.19 H[4..0]=08H���沨��

5.6 ����Y(ji��)������ͨ�^5.2��5.5�ķ��沨�η�����֪�����O(sh��)Ӌ(j��)�еĸ��(xi��ng)���܉�ܺõČ�(sh��)�F(xi��n)���ڕr��}�_�������£�Ӌ(j��)��(sh��)��CNTA��CNTB���ܰ��������O(sh��)���õ�Ҏ(gu��)�t�M(j��n)��Ӌ(j��)��(sh��)��CNTA�ǿɿصļӜpӋ(j��)��(sh��)����U_D������Ӌ(j��)��(sh��)�ķ���EN1�����O(sh��)�����ֵ����(d��ng)NE1�ɸ��ƽ׃?y��u)���ƽ�r����������O(sh��)��ֵ��CNTB��5λ���M(j��n)��Ӌ(j��)��(sh��)�������ڕr��}�_CLK0��������һֱ�Ӕ�(sh��)����(d��ng)���ӵ�32�r���Ԅӷ��ص�0�����¼Ӕ�(sh��)����·Ӌ(j��)��(sh��)��ͬ�r�ӵ���(sh��)�ֱ��^��LMP_COMPARE�ϣ���(d��ng)CNTB��ֵС���O(sh��)��ֵ�r����(sh��)�ֱ��^��ݔ�����ƽ����(d��ng)CNTB��ֵ�����O(sh��)��ֵ�r����(sh��)�ֱ��^��ݔ�����ƽ����˸�׃�O(sh��)��ֵ�Ĵ�С�Ϳ��Ը�׃PWM���εĴ�С��Ҳ���������늙C(j��)���{(di��o)�١�Z_F��늙C(j��)�ķ����I���x��PWM���ε��M(j��n)�뷽��(d��ng)���1�r��늙C(j��)���D(zhu��n)����֮�����D(zhu��n)������늙C(j��)�Ŀ��ƣ���������ݔ��˼��σɂ��c�T������늙C(j��)�Ć����cֹͣ������w�IJ������£�

��(d��ng)�����IZ_F�I�r��늙C(j��)���D(zhu��n)����D5.11�������_�I�r��늙C(j��)���D(zhu��n)����D5.12������(d��ng)�����ISTART�r��늙C(j��)�_ʼ��������D5.14�������_�r��늙C(j��)ֹͣ��������D5.15����ͨ�^���IEN1���]���c���_���Ը�׃H[4.0]��ֵ����D5.17��5.18��5.19���Ķ���׃ֱ��늙C(j��)��PWMռ�ձȣ��_(d��)����׃ֱ��늙C(j��)�ٶȵ�Ŀ�ġ�

���O(sh��)Ӌ(j��)����VHDL�O(sh��)Ӌ(j��)FPGA �}���{(di��o)�ƿ��Ʒ���, Ӌ(j��)��C(j��)����͌�ֱ��늙C(j��)���ƵĽY(ji��)������,ԓ�·����Ч�خa(ch��n)��PWM ������̖����늙C(j��)���D(zhu��n)��, ���ƾ�����FPGA �еĔ�(sh��)�ֱ��^���Q�����ڱ��O(sh��)Ӌ(j��)�У����õĔ�(sh��)�ֱ��^����5λ, �����Ӕ�(sh��)�ֱ��^����λ��(sh��), �Ϳ������늙C(j��)�D(zhu��n)�ٵĿ��ƾ��ȡ�

�·��ʡȥ��D/A �D(zhu��n)�Q��ʹ�·׃�ø��Ӻ���, ͬ�rҲ���Ϳ������ijɱ���FPGA ��(n��i)�����à�B(t��i)�C(j��)�Y(ji��)��(g��u), �����ɔ_�r, �ܺܿ�Į�����B(t��i)�D(zhu��n)������������B(t��i), ���C�˿���ϵ�y(t��ng)���иߵĿɿ��ԡ������ϵķ����п��Կ���������FPGA��ֱ��늙C(j��)�Ŀ����܉��_(d��)���ܺõ��A(y��)��Ч����

6 ���Y(ji��)�@���O(sh��)Ӌ(j��)�������������������ղ���Y�ϣ��ռ��Y�ϡ��������Y�ϵĻ��A(ch��)��������̼��g(sh��)�����������O(sh��)Ӌ(j��)�����M(j��n)��Փ�C��������������O(sh��)Ӌ(j��)���塣���@���g�������˃ɂ��µĕr�g������ԭ��D�ͳ���ֱ������ͷ�������M���O(sh��)Ӌ(j��)Ҫ�������ָ��(d��o)�ώ�X�ώ���ָ��(d��o)�£�����(j��)�΄�(w��)���A�M�������ԓ���I(y��)�O(sh��)Ӌ(j��)�����@���O(sh��)Ӌ(j��)���^���У��_��(sh��)Ҳ�����ܶ�����y��FPGA���g(sh��)��һ�T�^�µČW(xu��)�ƣ��@������Y�ϲ��Ǻܶ࣬���е�һ��ֻ�п��Լ�ȥ�������@��һ�����^���L���^�̡����������ώ�������˼·�����ǵ��D���^���W(w��ng)�ϲ���Y�ϣ��������ӌ�(sh��)�F(xi��n)늙C(j��)�����D(zhu��n)�ͷ��D(zhu��n)�����ٺ͜p�ٵȵȡ���(j��ng)�^ָ��(d��o)�ώ�X�ώ�������ָ�c(di��n)���B�m(x��)һ�����ڵĊ^��(zh��n)��������ϸ��Ұl(f��)�F(xi��n)�ի@�˲��٣�ͨ�^���Y���˽���ֱ��늙C(j��)����ԭ������;��PWM���Ƽ��g(sh��)���I�P�·�ӿڼ��g(sh��)���r��·���g(sh��)�ȵȣ�ͬ�rҲ�ҌW(xu��)��(x��)�F(xi��n)����Ӯa(ch��n)Ʒ���O(sh��)Ӌ(j��)���̣����Ժ���®a(ch��n)Ʒ�_�l(f��)����˻��A(ch��)��

���x

��Փ�ļ������֮�H��Ҳ�����ҵĴ�W(xu��)�����Ҫ�Y(ji��)���ĕr�˕r���ҵ�����o��ƽ�o�����_ʼ�M(j��n)���n�}��Փ�ĵ������ɣ����҂��ɾ���X�ώ��o�������ڵ�ָ��(d��o)��߀���������L���I(l��ng)��(d��o)��ͬ�W(xu��)�����ѽo���ҟo�ԵĎ��������@��Ո�������\�����x�⣡���@�ή��I(y��)�O(sh��)Ӌ(j��)�У�����Ҫ���x�ҵ�ָ��(d��o)�ώ�X���ڣ����ڌW(xu��)��(x��)���O(sh��)Ӌ(j��)����o���Ҵ�����ָ��(d��o)�������҂��ṩ��һ�����õČW(xu��)��(x��)�h(hu��n)�����ҌW(xu��)����֪�R�������˽�Q���}�ķ�����Ҳ�@���ˌ�(sh��)�`呟��ęC(j��)�������ć�(y��n)֔(j��n)��(x��)�¡�һ�z��ƈ�����L(f��ng)��һֱ���ҹ������W(xu��)��(x��)�еİ�ӣ�ͬ�r����ѭѭ���T�Ľ̌�(d��o)������һ���˼·�͞���̎����̹ʎҲ�o���ҟo�M�Ć��ϡ�����֮�⣬��߀����һЩ�����˵ĵ������ڴ�ףԸ�����w������ȫ���Ҹ���߀�кܶ��ҟo��һһ���e�����Ď��L�����˽o����ָ��(d��o)�͎������ڴ����ĵı�ʾ���x��������������һֱ�ӛ���ģ�������ĸ��x�ڰ�æ֮�г���r�g��醱�Փ�ĵČ��ҽ���

�D3.1 FPGAֱ��늙C(j��)PWM �����·

�D3.1 FPGAֱ��늙C(j��)PWM �����·