對(duì)于JTAG和SWD的使用區(qū)別,覺得下面這篇文章講的比較清晰了,所以轉(zhuǎn)帖到這里,希望對(duì)新手有所幫助。

SWD與JTAG區(qū)別及使用情況[轉(zhuǎn)載]

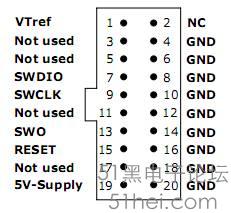

上圖是SEGGER說明書中給出的Jlink引腳圖,可以對(duì)照著看SWD引腳與JTAG引腳的關(guān)系。

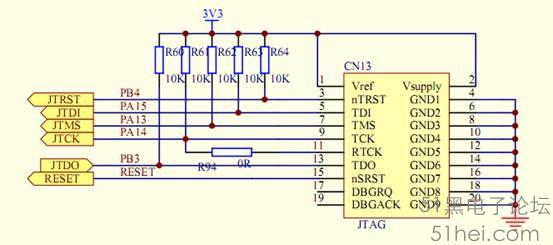

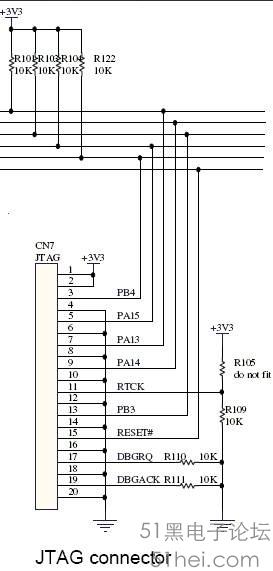

這是我手邊開發(fā)板上的JTAG連接圖,這個(gè)肯定是能用的。

這個(gè)是從網(wǎng)上找來的標(biāo)準(zhǔn)的JTAG連接圖,供對(duì)照參考。

調(diào)試方式既可以用JTAG,也可以用SWD。

以下是一段轉(zhuǎn)自:(showvi)

SWD 仿真模式概念簡(jiǎn)述

一、SWD 和傳統(tǒng)的調(diào)試方式區(qū)別

1. SWD 模式比 JTAG 在高速模式下面更加可靠。 在大數(shù)據(jù)量的情況下面 JTAG 下載程序會(huì)失敗, 但是 SWD 發(fā)生的幾率會(huì)小很多。基本使用 JTAG 仿真模式的情況下是可以直接使用 SWD 模式的, 只要你的仿真器支持。 所以推薦大家使用這個(gè)模式。

2. 在大家 GPIO 剛好缺一個(gè)的時(shí)候, 可以使用 SWD 仿真, 這種模式支持更少的引腳。

3. 在大家板子的體積有限的時(shí)候推薦使用 SWD 模式, 它需要的引腳少, 當(dāng)然需要的 PCB 空間就小啦! 比如你可以選擇一個(gè)很小的 2.54 間距的 5 芯端子做仿真接口。

二、仿真器對(duì) SWD 模式支持情況

1. 市面上的常用仿真器對(duì) SWD 模式支持情況

(1) JTAGV6 支持 SWD 仿真模式, 速度較慢。

(2) JTAGV7 比較好的支持 SWD 仿真模式, 速度有了明顯的提高,速度是 JTAGV6 的 6 倍。

(3) JTAGV8 非常好的支持 SWD 仿真模式, 速度可以到 10M。

(4) ULINK1 不支持 SWD 模式。

(5) 盜版 ULINK2 非常好的支持 SWD 模式, 速度可以達(dá)到 10M。

(6) 正版 ULINK2 非常好的支持 SWD 模式, 速度可以達(dá)到 10M。

2. SWD 硬件接口上的不同

(1) JTAGV6 需要的硬件接口為: GND, RST, SWDIO, SWDCLK

(2) JTAGV7 需要的硬件接口為: GND, RST, SWDIO, SWDCLK

(3) JTAGV8 需要的硬件接口為: VCC, GND, RST, SWDIO, SWDCLK (注:下面有我自己用JTAGV8的實(shí)際連線及相應(yīng)實(shí)驗(yàn)結(jié)果)

(4) ULINK1 不支持 SWD 模式

(5) 盜版 ULINK2 需要的硬件接口為: GND, RST, SWDIO, SWDCLK

(6) 正版 ULINK2 需要的硬件接口為: GND, RST, SWDIO, SWDCLK

由此可以看到只有 JTAGV8 需要 5 個(gè)引腳, 即多了一個(gè)VCC引腳,其好處是: 仿真器對(duì)目標(biāo)板子的仿真需要用到 RST 引腳, 使用仿真器內(nèi)部的 VCC 作這個(gè)功能其實(shí)并不是非常美妙。 因此,JTAGV8 選擇了只和目標(biāo)板共 GND, 但不共 VCC。 因此我覺得這種模式最合理, 當(dāng)然通常情況下仿真器和目標(biāo)板共 GND 和 VCC 是沒有錯(cuò)的。

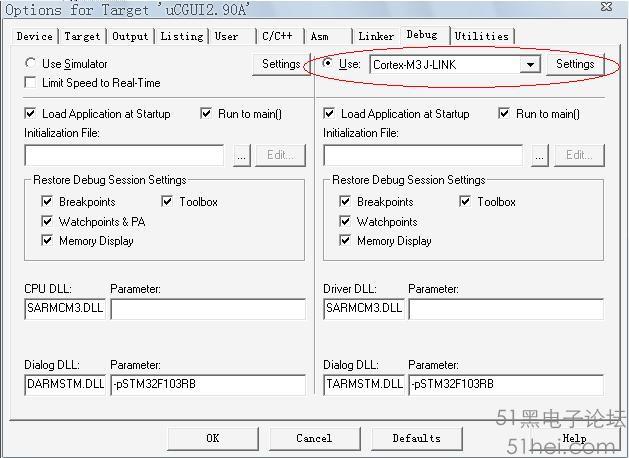

三、在 MDK 中SWD 模式的設(shè)置

在調(diào)試仿真的時(shí)候用JTAG的Cortex-M3方式已經(jīng)足夠,并且在MDK下他的功能已經(jīng)做得非常的好,用標(biāo)準(zhǔn)20腳的JTAG下載,速度是非常的快,一般初學(xué)者都是這樣做的。但是SWD方式似乎速度更快、更加方便、簡(jiǎn)捷、,對(duì)于項(xiàng)目中對(duì)板子空間要求嚴(yán)格、I/O口資源緊張的用戶來說更加的有利,正常的JTAG需要20管腳,而J-Link 的SWD只需要2根線(PA13/JTMS/SWDIO、PA14/JTCK/SWCLK)就夠了(加上電源線也就4根),這樣就節(jié)省了3個(gè)I/O口(PA15/JTDI、PB3/JTDO、PB4/JNTRST)為其它所用,并且可節(jié)省一部分板子的空間(只需4個(gè)口就可以了)。

下面我說一下SWD兩線仿真的一些步驟、注意事項(xiàng)及需要注意的問題。

接口的連接如下:將JTAG的1、7、9、20分別與自己的開發(fā)板上JTAG的VCC、JTMS、JTCK、GND用杜邦線相連即可!

接下來告訴大家怎么使用SWD設(shè)置:

打開工程OPTION設(shè)置:

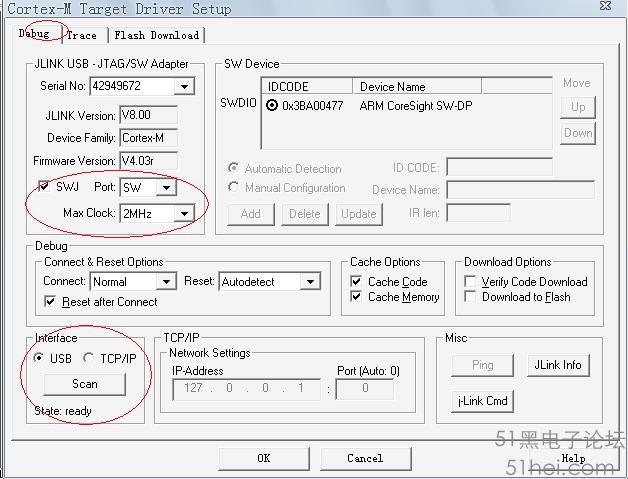

在設(shè)置中按照上圖設(shè)置成 SWD 模式, 速度你可以按照你的實(shí)際需求來設(shè)置, 如果你的板子供電系統(tǒng)不是特別穩(wěn)定, 紋波比較大或者仿真線比較長(zhǎng)可以設(shè)置成 500K 或者 1M,如果環(huán)境很好當(dāng)然可以選擇 10M , 當(dāng)然速度會(huì)飛起來。

記得不要忽略了左下方的那個(gè)USB還是 TCP 模式, 當(dāng)然我們是 USB 模式, 因?yàn)橛械臅r(shí)候默認(rèn)是 TCP 模式, 這個(gè)時(shí)候我們忽略這個(gè)設(shè)置后會(huì)仿真常常連接不上的。

/////轉(zhuǎn)載結(jié)束

下面是我自己的試驗(yàn)(用JTAG V8)

(1)按SW方式來調(diào)試,實(shí)際需要接1,7,9,15,20腳,某些資料上說的需要6個(gè)腳(第13腳SWO也需要連上)是不對(duì)的,SWO不需要連接。

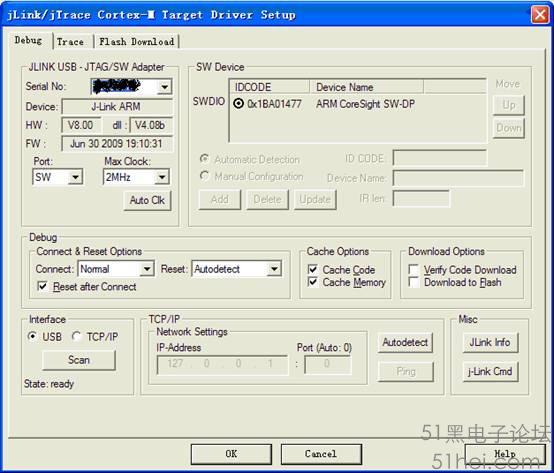

按上所述連接5個(gè)引腳時(shí)出現(xiàn)的畫面

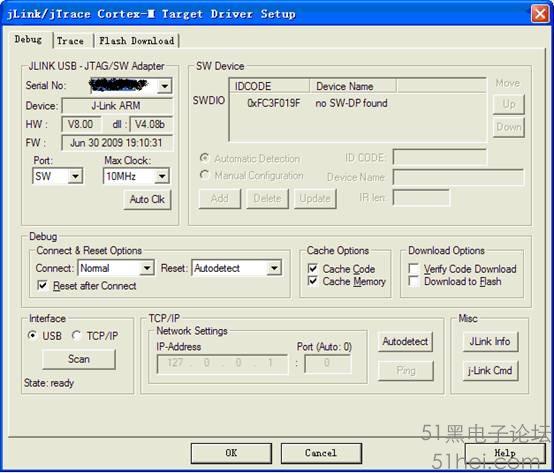

1腳不接時(shí)出現(xiàn)的畫面

(2)用兩種方式的速度沒有太大的區(qū)別。

再次測(cè)試:

(1)不接第15腳,即RESET腳,僅接4條引線,即Vref,SWDIO,SWCLK,GND。

(2)設(shè)置時(shí)Reset位選擇:AutoDetect,可以正常下載,仿真。

(3)如果Reset位選選擇:HW Reset ,則不能正常下載。

(4)速度遠(yuǎn)沒有上面轉(zhuǎn)載中說的那樣快,擦除和寫入ucosDemo工程約需40多s。以下是這個(gè)工程的代碼量:

Program Size: Code=96830 RO-data=143650 RW-data=1016 ZI-data=16440

但是有個(gè)現(xiàn)象,即下載一次后退出,然后再次進(jìn)入(沒有重編譯時(shí)),似乎沒有擦除和下載的過程,時(shí)間飛快。也許這就是上面所說的時(shí)間快的原因?

////以下來自21icbbs//

問:一直在核心板上玩 103ZE,都是些小程序 都是在RAM中調(diào)試的,而且只接三根線GND SWDIO SWCLK (VCC 直接接JTAG內(nèi)部的),很爽利。不過今天要試IIS 要放一個(gè)大的數(shù)據(jù)進(jìn)去,于是要燒到FLASH中去, 發(fā)現(xiàn)很快進(jìn)度條走完, 然后顯示失敗,放狗一搜,說要接RESET,于是接上,果然下進(jìn)去了...慘了,我PCB都畫好了,都只有4線(VCC SWDIO SWCLK GND),以后怎么辦呢?

答:可以不接,可以在MDK仿真器的設(shè)置里面不使用硬件復(fù)位,而是用system reset或者vect reset,前者適用的范圍更廣

/////轉(zhuǎn)載結(jié)束

JTAG引腳可以被復(fù)用為IO口,但是這樣一來,JTAG就不能夠連上芯片了。解決的方法有兩種:

(1)另寫一段程序,不要將JTAG復(fù)用為I/O口,然后將這段程序用串口工具寫入芯片中;

(2)將BOOT0/BOOT1設(shè)置成為內(nèi)部RAM啟動(dòng),那么上電后就不會(huì)執(zhí)行FLASH中的程序,這樣JTAG就能順利“接管”JTAG引腳。