|

電子科技大學(xué)實驗文檔

名稱數(shù)字邏輯電路實驗 實驗名稱基于一般模型的計數(shù)器設(shè)計 指導(dǎo)教師鄭* 學(xué)生姓名鄭* 學(xué)生學(xué)號17011737 學(xué)生班級 17040324 學(xué)生專業(yè)電子信息類 實驗日期 2018年6月 (1)熟悉計數(shù)器的一般模型 (2)掌握在QuartusII中實現(xiàn)計數(shù)器一般模型的方法。 (3)掌握自頂向下的電路設(shè)計方法。 (4)掌握使用FPGA實現(xiàn)時序電路的方法。 如果把計數(shù)器看作是輸出狀態(tài)隨時鐘信號不斷變化的狀態(tài)機,可以把它抽象成如圖5.2.1所示的一般結(jié)構(gòu)模型。在這個模型里,包含一個根據(jù)現(xiàn)態(tài)求得次態(tài)的狀態(tài)譯碼器,和一個由時鐘信號同步控制的n位寄存器組。

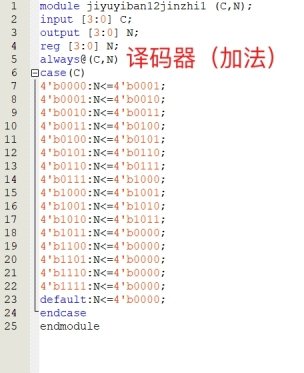

如果把計數(shù)器看作是輸出狀態(tài)隨時鐘信號不斷變化的狀態(tài)機,可以把它抽象成如圖5.2.1所示的一般結(jié)構(gòu)模型。在這個模型里,包含一個根據(jù)現(xiàn)態(tài)求得次態(tài)的狀態(tài)譯碼器,和一個由時鐘信號同步控制的n位寄存器組。 圖5.2.1 計數(shù)器的一般模型 在QuartusII中,無論是實現(xiàn)寄存器組模塊,還是實現(xiàn)譯碼器模塊,都是比較容易的。例如實現(xiàn)一個模16計數(shù)器,根據(jù)第四章實驗4.4廣義譯碼器的設(shè)計方法,可以寫Verilog HDL代碼實現(xiàn)。

首先創(chuàng)建新工程counter16,為新工程建立新文件夾counter16,命名工程和頂層文件名為counter16。點擊New|Verilog HDL File,新建文本文件,打開文本編輯窗口,鍵入Verilog HDL代碼,如圖5.2.2所示,生成CNT16元件。

圖5.2.2 狀態(tài)譯碼器

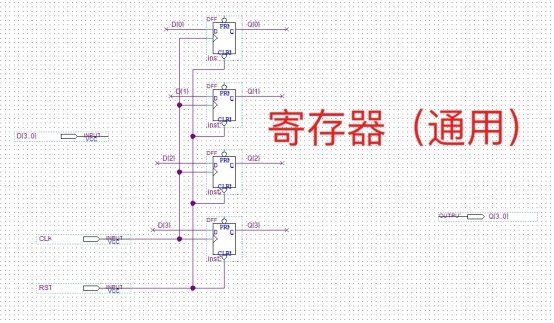

在這里,由于輸出狀態(tài)有4位,需要4個寄存器保存數(shù)據(jù),所以寄存器組模塊的電路圖如圖5.2.3所示。點擊New|Block Diagram/Schematic File,新建一個原理圖文件,命名為DFF4。在打開的圖形編輯窗口,放置4個dff元件,以及相應(yīng)的輸入輸出端口,連線。將所有的時鐘信號用統(tǒng)一的時鐘輸入信號CLK來控制,所有的清零信號,用RST來統(tǒng)一控制。命名好輸入輸出端口,4位寄存器組模塊就繪制好了,生成一個DFF4的元件。當(dāng)然也可以調(diào)用元件庫中的74175等集成的寄存器宏模塊實現(xiàn)電路。

然后再新建一個原理圖文件,命名為counter16,為頂層文件,和工程同名。調(diào)用CNT16和DFF4元件,按照計數(shù)器一般結(jié)構(gòu)模型連接兩個元件。注意模塊間傳輸多位數(shù)據(jù)時,點擊工具欄上的  符號,用總線進行連接。加上相應(yīng)的輸入和輸出端口,繪制頂層電路,如圖5.2.4所示。

圖5.2.3 DFF4寄存器組

圖5.2.4 計數(shù)器一般模型原理圖

設(shè)計計數(shù)器時,有時需要設(shè)計進位輸出或者借位輸出信號,因此增加一個進位信號,如下圖5.2.5所示。

圖5.2.5 進位輸出電路

電路原理圖繪制完成后,接下來是編譯、仿真和下載。仿真時,盡可能測試所有的輸入情況。例如在RST信號初期,用鼠標(biāo)左鍵拖曳的方式選中一段,置為低電平(有效,清零),后面置為高電平(無效,正常計數(shù)),如圖5.2.6所示,以觀察清零信號對輸出的影響。

圖5.2.6 對RST賦值

圖5.2.7是16進制計數(shù)器的仿真結(jié)果。由圖可見,在計數(shù)狀態(tài)到達1110時,進位輸出有一個毛刺。這是因為在輸出狀態(tài)從1011到1110變化時,變化時間不一致,導(dǎo)致有1111的信號短暫發(fā)生,因而出現(xiàn)了進位輸出端的毛刺。

圖5.2.7 16進制計數(shù)器仿真結(jié)果

在這個一般模型電路的基礎(chǔ)上,增加一個比較器模塊,可以實現(xiàn)反饋清零型的一般模型電路。例如實現(xiàn)一個模12計數(shù)器,電路模型圖如圖5.2.8所示。

圖5.2.8 基于一般模型的反饋清零型電路模塊圖

在QuartusII中畫出原理圖,如圖5.2.9所示。其中,譯碼器模塊和寄存器組和之前電路一模一樣。比較器模塊,用來比較現(xiàn)態(tài)CS和反饋清零預(yù)置數(shù)A,如果兩者相等,則清零;不相等,正常計數(shù)。

圖5.2.9 反饋清零的一般模型電路原理圖

比較器具體實現(xiàn)如下:

module comP(CS,A,R); //定義模塊名,及輸入輸出端口

input [3:0]CS,A;// 定義輸入端口,CS為現(xiàn)態(tài)輸出,A為預(yù)置清零狀態(tài)

output R;// 定義輸出端口,R為清零標(biāo)志數(shù)

reg R;// 輸出端口定義為reg類型

always@(CS,A,R)// always過程語句,當(dāng)CS、A、R發(fā)生變化,執(zhí)行后面的塊語句

case(CS) // case條件語句,這里也可以用if語句實現(xiàn)同樣的功能

A:R<=1'b1; // 當(dāng)CS等于A,R被賦值為1,這時反饋回寄存器,使輸出清零

default:R<=1'b0;// 當(dāng)CS不等于A,R被賦值為0,這時計數(shù)器正常計數(shù);

endcase // case語句結(jié)束

endmodule // 模塊結(jié)束

這個電路,可以通過修改清零預(yù)置數(shù)A,方便的更改計數(shù)模值,仿真結(jié)果如圖5.2.10所示。

圖5.2.10 反饋清零型一般模型電路的仿真結(jié)果 - 基于一般結(jié)構(gòu)模型,設(shè)計一個10進制加法計數(shù)器。使用QuartusII 完成創(chuàng)建工程、編輯電路圖、編譯,編輯波形文件仿真,記錄波形并說明仿真結(jié)果,最后在FPGA上進行硬件測試。

(2)根據(jù)計數(shù)器設(shè)計的一般模型,設(shè)計一個12進制加減法可逆計數(shù)器。使用QuartusII 完成創(chuàng)建工程、編輯電路圖、編譯,編輯波形文件仿真,記錄波形并說明仿真結(jié)果,最 FPGA上進行硬件測試  - 根據(jù)計數(shù)器設(shè)計的一般模型,設(shè)計初值可預(yù)置的計數(shù)器,變換預(yù)置數(shù)可使計數(shù)模值在2-20之間變化。使用QuartusII 完成創(chuàng)建工程、編輯電路圖、編譯,編輯波形文件仿真,記錄波形并說明仿真結(jié)果,最后在FPGA上進行硬件測試。

-

五.實驗總結(jié) 本次實驗先從最基本的一般模型設(shè)計計數(shù)器,按照一般模型的原理圖,先設(shè)計譯碼器對輸入信號進行編碼輸出譯碼后的信號給寄存器存儲數(shù)據(jù)。再根據(jù)要求,設(shè)計出正確的進位輸出。本次實驗在預(yù)習(xí)的電路原理圖設(shè)計與用語言設(shè)計譯碼器中出現(xiàn)不少問題。后不斷查閱資料,理解完畢,且在設(shè)計初值可預(yù)調(diào)的計數(shù)器實驗中,由于采取電路圖的方式難以成功實現(xiàn),故在此次實驗設(shè)計中采取了以HDL語言的形式進行編譯及仿真,并成功實現(xiàn)。而在實現(xiàn)引腳導(dǎo)入時未進行分頻,但在仿真中已成功實現(xiàn),且在位數(shù)上與理論設(shè)想相同。經(jīng)過這次實驗,我熟悉計數(shù)器的一般模型掌握在QuartusII中實現(xiàn)計數(shù)器一般模型的方法。掌握自頂向下的電路設(shè)計方法。掌握使用FPGA實現(xiàn)時序電路的方法。 六.思考題 在verilog設(shè)計中,給時序電路清0有兩種不同方法,它們是什么?如何實現(xiàn)? 同步復(fù)位和異步復(fù)位。同步復(fù)位是指與時鐘同步,當(dāng)復(fù)位信號有效之后,出現(xiàn)時鐘有效邊沿時才對電路模塊進行復(fù)位操作;而異步復(fù)位與時鐘信號無關(guān),只要復(fù)位信號有效,無論這時時鐘信號是什么樣,都對電路模塊進行復(fù)位操作。

以上圖文的Word格式文檔下載(內(nèi)容和本網(wǎng)頁上的一模一樣,方便大家保存):

|