|

|

FPGA����� ��ҹ���һ��

Ŀ�

��һ�� �wՓ 3

1.1 EDA��(ji��n)�� 3

1.2оƬ��B 4

1.3 Cyclone���Z�L(f��ng)��ϵ�н�B 4

�ڶ��� ģ�K��B 6

2.1�O(sh��)Ӌ(j��)���� 6

2.2Ӳ������ٷ��� 6

2.3 ��(l��)���Ԅ�(d��ng)�����C(j��)���� 6

2.4���w�O(sh��)Ӌ(j��)���� 6

2.5 �O(sh��)Ӌ(j��)���� 7

������ ���܄����cģ�K���� 8

3.1�Ԅ�(d��ng)����ģ�K 8

3.2 �Ԅ�(d��ng)�����O(sh��)Ӌ(j��)���� 8

3.3Ӳ�������ģ�K 8

3.3.1Ӳ��������O(sh��)Ӌ(j��)���� 9

3.3.2�O(sh��)Ӌ(j��)���E 9

������ �n���O(sh��)Ӌ(j��)ԭ�� 10

4.1Ӳ��������O(sh��)Ӌ(j��)ԭ�� 10

4.2��(l��)���Ԅ�(d��ng)�����O(sh��)Ӌ(j��)ԭ�� 10

4.3��ģ�K�Č�(sh��)�F(xi��n)���� 11

4.3.1�x����ģ�K��(sh��)�F(xi��n)���� 11

4.3.2�Ԅ�(d��ng)����ģ�K��(sh��)�F(xi��n)���� 11

4.3.3Ӳ�������ģ�K��(sh��)�F(xi��n)���� 12

������ ��(sh��)�(y��n)���O(sh��)Ӌ(j��) 13

5.1Ӳ�������ģ�K���� 13

5.2��(l��)���Ԅ�(d��ng)�����C(j��)���� 14

5.3 �x��ģ�K���� 18

5.4플��ļ����� 18

������ ��(sh��)�(y��n)�D���ļ� 20

6.1���_�i���D 20

6.2DXPԭ��D�����b 21

6.3�΄�(w��)�����r�f(shu��)�� 22

6.4Ӳ���B�ӈD 22

���Y(ji��) 25

�����īI(xi��n) 26

��䛣��(xi��ng)Ŀ��(sh��)��D 27

3.3.1Ӳ��������O(sh��)Ӌ(j��)����

��1������(j��)Ӳ�����������Ļ���ԭ���O(sh��)Ӌ(j��)���m��EDA���ԇ�(y��n)���Դ����ͨ�^(gu��)���lģ�K�õ�12MHZ�ľ���Դ����(xi��)��ɣ����g�{(di��o)ԇ���ڌ�(sh��)�(y��n)�����(y��n)�C�书�ܣ�

��2���(y��n)�Cģ�K�Ƿ�����Ɍ�(sh��)�`Ҫ������й��ܣ�Ȼ��ȥ�����lģ�K��������ģ�K���m��(d��ng)?sh��)��ĺ��g�{(di��o)ԇ�ɹ��������d��CPLD��(sh��)�(y��n)���ϡ�

3.3.2�O(sh��)Ӌ(j��)���E

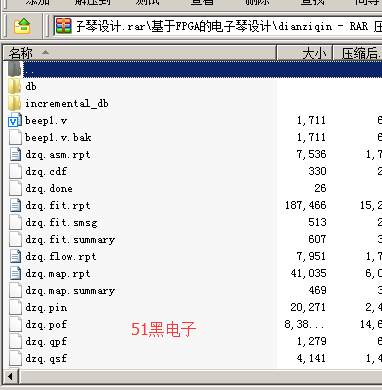

��1����Quarters II�н���һ��(g��)�����(xi��ng)Ŀ�ļ�beep1.qpf������ԓ�(xi��ng)Ŀ���½�Verilog HDLԴ�����ļ�beep1.v��ݔ�������a�����棬�M(j��n)�оC�Ͼ��g�����ھ��g�аl(f��)�F(xi��n)�e(cu��)�`���t�ҳ��������e(cu��)�`��ֱ�����g�ɹ���ֹ��

��2���x��Ŀ��(bi��o)�������M(j��n)�����_�i������δʹ�õĹ��_�O(sh��)�Þ����B(t��i)ݔ�롣

��3����(du��)ԓ�����ļ��M(j��n)��ȫ�̾��g̎�������ھ��g�^(gu��)���аl(f��)�F(xi��n)�e(cu��)�`���t�ҳ��������e(cu��)�`��ֱ�����g�ɹ���ֹ��

��4�����a(ch��n)����beep1.sofݔ����(du��)FPGA�M(j��n)�����á����°��IKEY1~KEY8�Ϳ����_(k��i)ʼʹ������ف�(l��i)��������(l��)�ˡ�

ȫ���Y��51hei���d��ַ��

����FPGA��������O(sh��)Ӌ(j��).rar

(5.14 MB, ���d��(sh��): 152)

����FPGA��������O(sh��)Ӌ(j��).rar

(5.14 MB, ���d��(sh��): 152)

2019-1-6 20:09 �ς�

�c(di��n)���ļ������d����

|

�u(p��ng)��

-

�鿴ȫ���u(p��ng)��

|

����TQQ:125739409;���g(sh��)����QQȺ281945664

����TQQ:125739409;���g(sh��)����QQȺ281945664