|

實(shí)驗(yàn)四、七人表決器的設(shè)計(jì)實(shí)驗(yàn)報(bào)告 一、實(shí)驗(yàn)?zāi)康?/strong> 1、初步了解Verilog語(yǔ)言。 2、學(xué)會(huì)用Verilog語(yǔ)言的行為描述方式來(lái)設(shè)計(jì)電路。 二、實(shí)驗(yàn)原理 用七個(gè)開關(guān)作為表決器的7個(gè)輸入變量,輸入變量為邏輯“1”時(shí)表示表決者“贊同”;輸入變量為邏輯“0”時(shí),表示表決者“不贊同”。輸出邏輯“1”時(shí),表示表決“通過(guò)”;輸出邏輯“0”時(shí),表示表決“不通過(guò)”。當(dāng)表決器的七個(gè)輸入變量中有4個(gè)以上(含4個(gè))為“1”時(shí),則表決器輸出為“1”;否則為“0”。 七人表決器設(shè)計(jì)方案很多,比如用多個(gè)全加器采用組合電路實(shí)現(xiàn)。用VHDL語(yǔ)言設(shè)計(jì)七人表決器時(shí),也有多種選擇。我們可以用結(jié)構(gòu)描述的方式用多個(gè)全加器來(lái)實(shí)現(xiàn)電路,也可以用行為描述。采用行為描述時(shí),可用一變量來(lái)表示選舉通過(guò)的總?cè)藬?shù)。當(dāng)選舉人大于或等于4時(shí)為通過(guò),綠燈亮;反之不通過(guò)時(shí),黃燈亮。描述時(shí),只須檢查每一個(gè)輸入的狀態(tài)(通過(guò)為“1”,不通過(guò)為“0”),并將這些狀態(tài)值相加,判斷狀態(tài)值和即可選擇輸出。 三、實(shí)驗(yàn)內(nèi)容 1、用Verilog語(yǔ)言設(shè)計(jì)七人表決器(VHDL程序代碼可附在實(shí)驗(yàn)報(bào)告后面)。 2、下載并驗(yàn)證結(jié)果。 四、實(shí)驗(yàn)結(jié)果 1、畫出你設(shè)計(jì)的七人表決器的仿真波形圖。 <一>方案比較: 消抖方式: - <font color="rgb(0, 0, 0)">always@(posedge clk or posedge rst)

- begin

- if(rst)

- begin

- sum<=0;

- date_in<=0;

- end

- else

- begin

- if(in)

- begin

- yl<=yl+1;

- if(js==5'b11111) //按鍵消抖

- begin

- yl<=0;

- sum=0;

- date_in<=date_in | in;

- sum=0;

- for(i=0;i<7;i=i+1)

- if(date_in[i])

- sum=sum+1;

- end

- end

- end

- end</font>

延時(shí)消抖: always@(posedge clk or posedge rst) begin if(rst) cnt<=20'd0; else if(vote) cnt<=20'd0; else begin cnt<=cnt+1'b1; end end 結(jié)論:第一個(gè)消抖方法可以達(dá)到內(nèi)外消抖,第二個(gè)就是一個(gè)很簡(jiǎn)單的延時(shí)消抖,很容易理解。 always@(vote or rst) begin if(rst) begin sum<=0; end else sum<=vote[6]+vote[5]+vote[4]+vote[3]+vote[2]+vote[1]+vote[0]; end 結(jié)論:第一7bit數(shù)相加,統(tǒng)計(jì)投票的人數(shù),第二,利用for 循環(huán)來(lái)完成投票人數(shù)的統(tǒng)計(jì)。 <二>硬件測(cè)試 2.1管腳約束 Out:pin-127 show:pin-133 Pin-126 pin-135 Pin-125 pin-136 Din:pin-32 pin-137 Pin-33 pin-138 Pin-34 pin-141 Pin-38 pin-142 Pin-39 pin-128 Pin-42 Pin-43 Pin-44 2.2 quarters ll操作平臺(tái)以及試驗(yàn)箱 <三>軟件測(cè)試 always@(vote or rst) begin if(rst) begin sum<=0; end else sum<=vote[6]+vote[5]+vote[4]+vote[3]+vote[2]+vote[1]+vote[0]; end end 這段是利用7bit的數(shù)相加來(lái)得到投票通過(guò)的人數(shù) always@(posedge clk or posedge rst) begin if(rst) cnt<=20'd0; else if(vote) cnt<=20'd0; else begin cnt<=cnt+1'b1; end end 這段是利用延時(shí)消抖 always@(posedge clk or posedge rst) begin if(rst) begin out<=3'b111; count<=0; end else begin case(count) 0 : begin out<=3'b110; case (sum[2:0]) 3'b000:show <= 8'b11111100; 3'b001:show <= 8'b01100000; 3'b010:show <= 8'b11011010; 3'b011:show <= 8'b11110010; 3'b100:show <= 8'b01100110; 3'b101:show <= 8'b10110110; 3'b110:show <= 8'b10111110; 3'b111:show <= 8'b11100000; endcase count<=count+1; end 1 : begin out<=3'b111; if(sum>=4) show<=8'b01100000; else show<=8'b11111100; count<=count+1; end endcase end end endmodule 這段是片選兩個(gè)數(shù)碼管,一個(gè)數(shù)碼管用來(lái)顯示投票的人數(shù),一個(gè)顯示大于等于四個(gè)人時(shí)用1表示通過(guò),其他情況則為零。

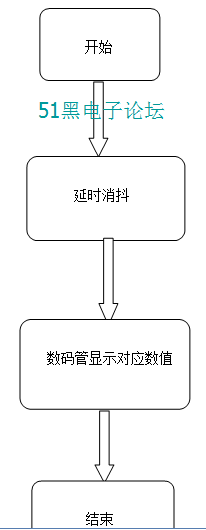

<四>實(shí)驗(yàn)流程圖

<五>七人表決器源程序 module test4(vote,show,out,rst,clk); input rst,clk; output reg [2:0]out; output reg[7:0]show; input [6:0] vote; reg[19:0] cnt; reg [2:0]sum; reg count; integeri;//定義整型變量i為循環(huán)控制變量 always@(vote or rst) begin if(rst) begin sum<=0; end else sum<=vote[6]+vote[5]+vote[4]+vote[3]+vote[2]+vote[1]+vote[0]; end always@(posedge clk or posedge rst) begin if(rst) cnt<=20'd0; else if(vote) cnt<=20'd0; else begin cnt<=cnt+1'b1; end end always@(posedge clk or posedge rst) begin if(rst) begin out<=3'b111; count<=0; end else begin case(count) 0 : begin out<=3'b110; case (sum[2:0]) 3'b000:show <= 8'b11111100; 3'b001:show <= 8'b01100000; 3'b010:show <= 8'b11011010; 3'b011:show <= 8'b11110010; 3'b100:show <= 8'b01100110; 3'b101:show <= 8'b10110110; 3'b110:show <= 8'b10111110; 3'b111:show <= 8'b11100000; endcase count<=count+1; end 1 : begin out<=3'b111; if(sum>=4) show<=8'b01100000; else show<=8'b11111100; count<=count+1; end endcase end end endmodule 2、簡(jiǎn)單描述你設(shè)計(jì)的七人表決器下載到試驗(yàn)箱上的結(jié)果。(手寫) 片選了兩個(gè)數(shù)碼管,第一個(gè)數(shù)碼管當(dāng)投票人數(shù)小于4的時(shí)候,顯示0。每撥下一個(gè)開關(guān),第二個(gè)數(shù)碼管顯示的數(shù)字按照123順序遞增,當(dāng)投票人數(shù)大于等于4的時(shí)候,第一個(gè)數(shù)碼管有0變成1,但是第二個(gè)數(shù)碼管現(xiàn)實(shí)的數(shù)字按照4567順序遞增。 五、實(shí)驗(yàn)小結(jié)(手寫) 通過(guò)這段時(shí)間的EDA實(shí)驗(yàn),我更加熟練地掌握了EDA開發(fā)的基本流程,熟練地使用Quartus ll軟件進(jìn)行編程,在自己的努力下,完成了七人表決器的相關(guān)設(shè)計(jì),感謝老師和同學(xué)給我的幫助。同時(shí),我發(fā)現(xiàn)了自己的編程思路還不是很清晰,需要在以后的學(xué)習(xí)中加強(qiáng)鍛煉。此次實(shí)驗(yàn)收獲很多,學(xué)會(huì)了延時(shí)消抖,對(duì)case語(yǔ)句的使用越來(lái)越熟練,這個(gè)程序雖然耗費(fèi)了一些時(shí)間來(lái)寫,但是在這個(gè)反復(fù)修改的過(guò)程中,我學(xué)習(xí)到了一些新東西,在驗(yàn)收實(shí)驗(yàn)的過(guò)程中,也逐漸意識(shí)到對(duì)于語(yǔ)法規(guī)范性的重要性,以及編程過(guò)程中寫程序的格式的規(guī)范性。

完整的Word格式文檔51黑下載地址:

實(shí)驗(yàn)四指導(dǎo)書七人表決器.doc

(128.5 KB, 下載次數(shù): 93)

實(shí)驗(yàn)四指導(dǎo)書七人表決器.doc

(128.5 KB, 下載次數(shù): 93)

2017-11-23 14:39 上傳

點(diǎn)擊文件名下載附件

eda課程設(shè)計(jì)

|